# Fault Allocation in Multilevel Converter Statcoms

B.Bansiraj<sup>1</sup>, M. Lokya<sup>2</sup>

<sup>1</sup>Final M.Tech student, Dept of EEE,MIST, Sathupally, India, <sup>2</sup>Asst. Professor, Dept of EEE, MIST, Sathupally,India,

Abstract: This paper introduces an approach to detect the existence of the faulted switch, identify which switch is faulty, and reconfigure the STATCOM. This approach is illustrated on an eleven-level STATCOM and the effect on the dynamic performance and the total harmonic distortion (THD) is analyzed Many static synchronous compensators (STATCOMs) utilize multilevel converters due to the following: 1) lower har- monic injection into the power system; 2) decreased stress on the electronic components due to decreased voltages; and 3) lower switching losses. One disadvantage, however, is the increased like- lihood of a switch failure due to the increased number of switches in a multilevel converter. Due to its unique topology, the Modular Multilevel STATCOM has many advantages but requires a sophisticated controller and puts higher requirements on simulation tools. To simulate the STATCOM in real-time is preferable because it enables hardware-in-the-loop test of the system in various scenarios including extreme fault conditions, which cannot be tested on a real STATCOM. A single switch failure, however, does not necessarily force an (2n + 1)-level STATCOM offline. Even with a reduced number of switches, a STATCOM can still provide a significant range of control by removing the module of the faulted switch and continuing with (2n - 1) levels.

Index Terms: Fault detection, multilevel converter, static synchronous compensator (STATCOM)

## I. INTRODUCTION

THE static synchronous compensator (STATCOM) has been well accepted as a power system controller for im- proving voltage regulation and reactive compensation [1]–[5]. There are several compelling reasons to consider a multilevel converter topology for the STATCOM [6]–[8]. These well-known reasons include the following: 1) lower harmonic injec- tion into the power system; 2) decreased stress on the electronic components due to decreased voltages; and 3) lower switching losses [9]. Various multilevel converters also readily lend them- selves to a variety of PWM strategies to improve efficiency and control. An eleven-level cascaded multilevel STATCOM is shown in Fig. 1. This converter uses several full bridges in series to synthesize staircase waveforms. Because every full bridge can have three output voltages with different switching combinations, the number of output voltage levels is 2n + 1 where *n* is the number of full bridges in every phase. The converter cells are identical and therefore modular.

As higher level converters are used for high output rating power applications, a large number of power switching devices will be used. Each of these devices is a potential failure point. Therefore, it is important to design a sophisticated control to produce a fault-tolerant STATCOM. A faulty power cell in a cascaded H-Bridge STATCOM can potentially cause switch modules to explode [10] leading to the fault conditions such as a short circuit or an overvoltage on the power system resulting in an expensive down time [11]. Subsequently, it is crucial to iden- tify the existence and location of the fault for it to be removed. Several fault detection methods have been proposed over the last few years [10]–[18]. Resistor sensing, current trans formation, and  $V_{CE}$  sensing are some of the more common approaches. For example, a method based on the output current behavior is used to identify IGBT short circuits [12]. The primary drawback with the proposed approach is that the fault detection time depends on the time constant of the load. There- fore, for loads with a large RL time constant, the faulty power cell can go undetected for numerous cycles, potentially leading to circuit damage. Another fault detection approach proposed in [13] is based on a switching frequency analysis of the output phase voltage. This method was applied to flying capacitor converters and has not been extended to cascaded converters. AI-based methods were proposed to extract pertinant signal features to detect faults in [14]. In [15], sensors are used to measure each IGBT current and to initiate switching if a fault is detected.

A fault-tolerant neutral point-clamped converter was proposed in [16]. In [17], a reconfiguration system based on bidirectional switches has been designed for three-phase asym- metric cascaded H-bridge inverters. The fundamental output voltage phase shifts are used to rebalance a faulted multilevel cascaded converter in [18].

Fig. 1. Eleven-level cascaded multilevel STATCOM.

#### International Journal of Modern Engineering Research (IJMER)

## <u>www.ijmer.com</u> Vol.2, Issue.5, Sep-Oct. 2012 pp-3947-3955 ISSN: 2249-6645

In this paper, the method we propose requires only that the output dc link voltage of each phase be measured. This measurement is typically accomplished anyway for control purposes. If a fault is detected, the module in which the fault occurred is then isolated and removed from service. This approach is consistent with the modular design of cascaded converters in which the cells are designed to be interchangeable and rapidly removed and replaced. Until the module is replaced, the multilevel STATCOM continues to operate with slightly decreased, but still acceptable, performance. In summary, this approach offers the following advantages:

- > No additional sensing requirements;

- Additional hardware is limited to two by-pass switches per module;

- > The dynamic performance and THD of the STATCOM is not significantly impacted.

## **II.** MULTILEVEL STATCOM

A cascaded multilevel STATCOM contains several H-bridges in series to synthesize a staircase waveform. The inverter legs are identical and are therefore modular. In the eleven-level STATCOM, each leg has five H-bridges. Since each full bridge generates three different level voltages (V, 0, -V) under differ-

ent switching states, the number of output voltage levels will be eleven. A multilevel configuration offers several advantages over other converter types [19].

- 1) It is better suited for high-voltage, high-power applications than the conventional converters since the currents and voltages across the individual switching devices are smaller.

- 2) It generates a multistep staircase voltage waveform ap- proaching a more sinusoidal output voltage by increasing the number of levels.

- 3) It has better dc voltage balancing, since each bridge has its own dc source.

To achieve a high-quality output voltage waveform, the volt- ages across all of the dc capacitors should maintain a constant value. Variations in load cause the dc capacitors to charge and discharge unevenly leading to different voltages in each leg of each phase. However, because of the redundancy in switching states, there is frequently more than one state that can synthesize any given voltage level. Therefore, there exists a "best" state among all the possible states that produces the most balanced voltages [20]. Since there are multiple possible switching states that can be used to synthesize a given voltage level, the particular switching topology is chosen such that the capacitors with the lowest voltages are charged or conversely, the capacitors with the highest voltages are discharged. This redundant state selection approach is used to maintain the total dc link voltage to a near constant value and each individual cell capacitor within a tight bound.

Different pulse width modulation (PWM) techniques have been used to obtain the multilevel converter output voltage. One common PWM approach is the phase shift PWM (PSPWM) switching concept [21]. The PSPWM strategy causes cancella- tion of all carrier and associated sideband harmonics up to the

(N - 1)th carrier group for an N-level converter. Each carrier

signal is phase shifted by

$$\Delta \varphi = \frac{2\pi}{2\pi}$$

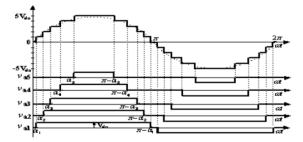

Where *n* is the number of cells in each phase. Fig. 2 illustrates the carrier and reference waveforms for a phase leg of the eleven-level STATCOM. In this figure, the carrier frequency has been decreased for better clarity. Normally, the carrier frequency for PWM is in the range of 1-10 kHz.

Fig. 2. (a) Carrier and reference waveform for PSPWM. (b) Output waveform.

## International Journal of Modern Engineering Research (IJMER) www.ijmer.com Vol.2, Issue.5, Sep-Oct. 2012 pp-3947-3955 ISSN: 2249-6645

## III. ANALYSIS OF FAULT FOR THE MULTILEVEL STATCOM

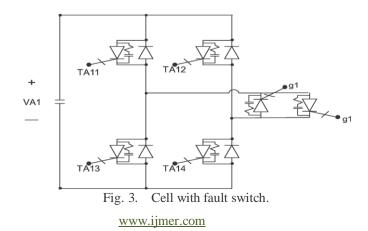

A converter cell block, as shown in Fig. 3, can experience

several types of faults. Each switch in the cell can fail in an open or closed state. The closed state is the most severe failure since it may lead to shoot through and short circuit the entire cell. An open circuit can be avoided by using a proper gate circuit to control the gate current of the switch during the failure [23]. If a short circuit failure occurs, the capacitors will rapidly discharge through the conducting switch pair if no protective action is taken. Hence, the counterpart switch to the failed switch must be quickly turned off to avoid system collapse due to a sharp current surge. Nomenclature for the proposed method is given in Table I.

The staircase voltage waveform shown in Fig. 2 is syn- the sized by combining the voltages of the various cells into the desired level of output voltage. At the middle levels of the voltage waveform, due to the switching state redundancy, there are more than one set of switching combinations that may be used to construct the desired voltage level. Therefore, by varying the switching patterns, the loss of any individual cell

#### TABLE I NOMENCLATURE

| Eout                                                                   | STATCOM output voltage (V)                                                                                                                         |  |  |  |  |  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| $ \begin{array}{c} \hat{E}_{out} \\ E' \\ S_{j1}, S_{j2} \end{array} $ | Filtered STATCOM output voltage (RMS) (V)                                                                                                          |  |  |  |  |  |  |

| E'                                                                     | STATCOM threshold voltage (constant) (V)                                                                                                           |  |  |  |  |  |  |

| $S_{i1}, S_{i2}$                                                       | $S_{j2}$ Switching signal of the <i>j</i> -th cell (0, 1)                                                                                          |  |  |  |  |  |  |

| $f_i$ possible STATCOM output voltage (V)                              |                                                                                                                                                    |  |  |  |  |  |  |

| $x_i$ difference between possible and actual STATCOM output (V)        |                                                                                                                                                    |  |  |  |  |  |  |

| $g_j$ bypass signal for <i>j</i> -th cell (0, 1)                       |                                                                                                                                                    |  |  |  |  |  |  |

|                                                                        |                                                                                                                                                    |  |  |  |  |  |  |

| -                                                                      | $V_{AI}^{+} - V_{A2}^{+} - V_{A3}^{+} - V_{A4}^{+} - V_{A5}^{+}$ $A_{I} \qquad A_{2} \qquad A_{3} \qquad A_{4} \qquad A_{5} \qquad E_{out, a}^{+}$ |  |  |  |  |  |  |

| L                                                                      |                                                                                                                                                    |  |  |  |  |  |  |

|                                                                        | $B_1$ $B_2$ $B_3$ $B_4$ $B_5$ $E_{out, b}$                                                                                                         |  |  |  |  |  |  |

| <u> </u>                                                               | $C_1$ $C_2$ $C_3$ $C_4$ $C_5$ $E_{out, c}$                                                                                                         |  |  |  |  |  |  |

Fig. 4. Simplified eleven-level cascaded multilevel STATCOM.

will not significantly impact the middle voltages of the output voltage. However, the peak voltages require that all cells contribute to the voltage; therefore, the short circuit failure of any one cell will lead to the loss of the first and (2n + 1) output levels and cause degradation in the ability of the STATCOM to produce the full output voltage level.

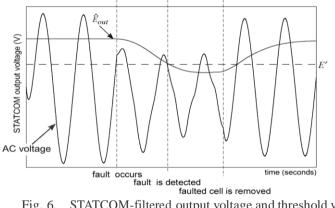

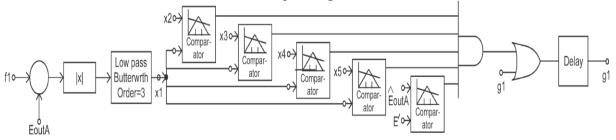

Consider the simplified eleven-level converter shown in Fig. 4. The process for identifying and removing the faulty cell block is summarized in Fig. 5. The input to the detection algorithm is  $\hat{E}_{OUL}$  for each phase, where  $\hat{E}_{OUL}$  is the STATCOM-filtered RMS output voltage. If the STATCOM RMS output voltage drops below a preset threshold value (*E*), then, a fault is known to have occurred (see Fig. 6).

Once a fault has been detected to have occurred, then, the next step is to identify the faulty cell. By utilizing the switching signals in each converter cell, (i.e.,  $S_1$  and  $S_2$ ), it is possible to calculate all of the possible voltages that can be produced at any given instant as illustrated in Table II (terminology adopted from [23]): Thus, the output voltage of a cell is

Thus, the output voltage of a certain - (1)

$$v_{ax} = v_{ax} + -v_{ax}$$

and since the cells of the STATCOM are serially connected, the total output voltage per phase is

$$v_{y0} = \sum_{x=1}^{n} v_{yx}, \qquad y \in [a, b, c]$$

where *n* is the number of blocks.By utilizing the switching signals in each converter cell, (i.e.,  $S_{j1}$  and  $S_{j2}$ , *j* is the cell number), it is possible to calculate all of the possible voltages that can be produced at any given instant. When there is a fault in the multilevel converter, the capacitor at the faulty block will rapidly discharge. This discharge results in a phase shift in the output ac voltage as well as a change in amplitude of voltage.

| ГĘ | E AND OUTPUT VOLTAGE |       |            |            |                 |  |  |

|----|----------------------|-------|------------|------------|-----------------|--|--|

| [  | $S_1$                | $S_2$ | $v_{ax}^+$ | $v_{ax}^-$ | $v_{ax}$        |  |  |

| ſ  | 0                    | 0     | 0          | 0          | 0               |  |  |

|    | 0                    | 1     | 0          | $v_{dc}$   | $-v_{dc}$       |  |  |

|    | 1                    | 0     | $v_{dc}$   | 0          | v <sub>dc</sub> |  |  |

|    | 1                    | 1     | $v_{dc}$   | $v_{dc}$   | 0               |  |  |

## TABLE II SWITCHING STATE AND OUTPUT VOLTAGE OF AN H-BRIDGE

Flowchart for eleven-level converter. Fig. 5.

Fig. 6. STATCOM-filtered output voltage and threshold value.

The set of all possible phase fault voltages for an eleven-level converter is given by  $f_1 = V_{dc0} (S_{21} - S_{22} + S_{31} - S_{32} + S_{41} - S_{42} + S_{51} - S_{52})$  (cell 1 faulted)  $f_2 = V_{dc0} (S_{11} - S_{12} + S_{31} - S_{32} + S_{41} - S_{42} + S_{51} - S_{52})$  (cell 2 faulted)

$f5 = V_{dc0} (S_{11} - S_{12} + S_{21} - S_{22} + S_{31} - S_{32} + S_{41} - S_{42})$  (cell 5 faulted) or more succinctly as

$$f_i = V_{\rm dc0} \sum_{\substack{j=1\\j\neq i}}^n (S_{j1} - S_{j2}), \qquad i = 1, \dots, n \tag{3}$$

where  $V_{dc0}$  is the ideal voltage across a single cell block. If there is a faulted cell, only one  $f_i$  will be near the actual STATCOM output phase voltage  $E_{\text{OUT}}$ ; all of the others will be too high. Therefore, to determine the location of the fault cell, each  $f_i$  is compared against  $E_{out}$  to yield

$$x_i = |E_{\text{out}} - f_i|, \quad i = 1, ..., n.$$

(4)

The smallest  $x_i$  indicates the location of the faulted block because this indicates the  $f_i$  which most closely predicts the actual  $E_{out}$ . The choice of threshold voltage  $E_{out}$  depends on the number of cells in the converter. The ideal output voltage is

$$\hat{E}_{\text{out},0} = \frac{nV_{\text{dc}0}}{\sqrt{2}}.$$

During a fault,  $E_{out}$  will decrease by  $V_{dc0}$  yeilding

$$\hat{E}_{\text{out,fault}} = \frac{(n-1)V_{\text{dc0}}}{\sqrt{2}} = \frac{n-1}{n}\hat{E}_{\text{out,0}}.$$

Therefore, the threshold voltage E should be chosen such that  $(n - 1/n)E_{out,0} \leq E \leq E_{out,0}$ . In an elevenlevel converter, n = 5 and the faulted RMS voltage will decrease by roughly 20%. Therefore, a good choice for E is 85%

www.ijmer.com Vol.2, Issue.5, Sep-Oct. 2012 pp-3947-3955 ISSN: 2249-6645 of the rated output STATCOM voltage.

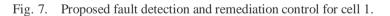

The last step is to actuate the module bypass switch  $g_i$  shown in Fig. 3. A slight time delay is added to the logic to neglect for momentary spikes that may occur. It is desirable to neglect momentary sags in the dc link voltage, but respond to sags of increased duration that indicate a faulted module. Fig. 7 shows the realization logic for the proposed fault detection and module removal method.

The use of a fault handling switch in multilevel converters is not uncommon. In a fault handling switch is used in a fly- ing capacitor multilevel inverter. While the additional circuitry does increase the cost of the circuit, it also increases the relia- bility be enabling the circuit to keep working (albeit at a slightly reduced operating range) until the module can be replaced.

#### IV. RESULTS

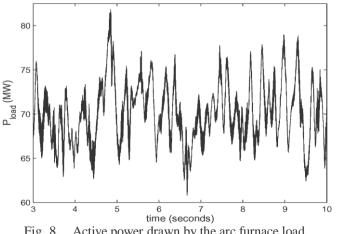

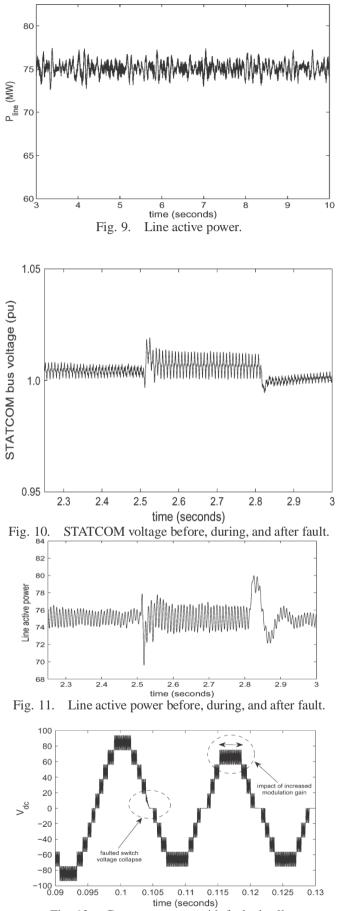

The single line diagram of the electrical distribution system feeding an arc furnace is shown in Fig. 8. The STATCOM has been shown to be an efficient controller to mitigate arc furnace flicker [27]. The electrical network consists of a 115-kV generator and an impedance that is equivalent to that of a large network at the point of common coupling (PCC). The STATCOM is connected to the system through a Y-Delta transformer. The system was simulated using PSCAD/EMDTC. The electrical arc furnace load is non sinusoidal, unbalanced, and randomly fluctuating. Electric arc furnaces are typically used to melt steel and will produce current harmonics that are random. In addition to the integer harmonics, arc furnace currents are rich in inter harmonics [24]. The flicker waveform has sub synchronous variations in the 5–35-Hz range [25]. Fig. 9 shows the active power drawn by the arc furnace. Note that the STATCOM is able to improve the line active power such that active power variations caused by the arc furnace do not propagate throughout the system as shown in Fig. 10. The simulation model and control scheme is described in detail in [28]. The dc capacitor voltages normally vary and are kept in relative balance through redundant state selection [20].

#### A. Dynamic Performance

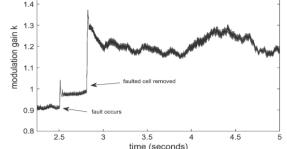

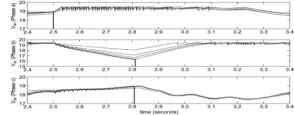

To test the proposed fault detection and mitigation approach, a faulty switch was initiated at 2.5 s. Within 300 ms, the fault has been detected, the module removed, and the STATCOM restored to steady-state operation. This fault duration is longer than is necessary; the fault was intentionally left on to better illustrate its effect on the system and removal. The STATCOM bus voltage and line active powers are shown before the fault, during, and after the faulty module is removed (Figs. 11 and 12). Note that both the bus voltage and line active power are adversely affected during the fault. In both cases, the high frequency oscillations are increased. Once the faulty module is removed, the system returns to its pre-fault behavior. There is a small induced low-frequency oscillation that can be observed in the line active power, but this is rapidly damped by the STATCOM's control.

The average dc link voltage before, during, and after the fault is shown in Fig. 13. During the fault, the dc voltage drops rapidly as the faulted module capacitor discharges. When the faulty module is removed, the average dc voltage drops to roughly 80% of the initial voltage, as expected. The continued variation in the dc link voltage is due to the continual variation of the arc furnace load that the STATCOM is compensating and is normal.

Fig. 8. Active power drawn by the arc furnace load.

Fig. 12. Converter output with faulted cell.

Fig. 13. Modulation gain k before, during, and after fault.

Fig. 14. Individual module capacitor voltages before, during, and after fault.

Fig. 15. Percent harmonic content of the faulty phase before, during, and after fault.

Fig. 14 shows two cycles of the STATCOM multilevel volt- age output. There are several important aspects of this output waveform that have been highlighted. First, note the voltage collapse of the first level due to the faulted cell. This collapse in voltage will occur at the level that corresponds to the faulty cell. It is not possible to directly correlate the level number with the cell number (i.e., a collapse in level four does not necessarily indicate a fault in cell 4) because of the redundant state selection scheme that is used to balance the capacitor voltages.

A further aspect of note is the increase in length of the top- level duration. This is due to the increase in the modulation gain k due to the decrease in dc link voltage. Since the STATCOM output voltage is directly proportional to

$V_{\text{stat}} = kV_{\text{dc}} \cos \alpha$

Where k is the modulation gain and  $\alpha$  is the phase angle. If  $V_{dc}$  decreases by 20%, then, k must increase by 20% to compensate. An increase of this magnitude in modulation gain takes the PWM into over modulation where the magnitude of the reference waveform exceeds the magnitude of the carrier. This results in an increased length of time at higher voltage levels. Over modulation may also result in the increase of lower frequency harmonics. The modulation gain k is shown in Fig. 15. The individual module capacitor voltages in each phase for a faulty a phase switch are shown in Fig. 16. Note that the faulted module voltage decays rapidly at 2.5 s (when the fault was applied). The remaining capacitor voltages in phase a show significant "chopping" as the redundant state selection approach rapidly alternates between modules to maintain the average dc link voltage. A crowbar circuit is used with each module to limit the maximum dc voltage, leading to the chopping behavior. Phase b shows a continual decline in all of the capacitor voltages until the corresponding faulty module is removed at 2.8 s. The capacitor voltages increase until they are in the nominal range and then exhibit similar "chopping" until they are regulated. Phase c does not exhibit chopping because all of the individual cell voltages are of similar magnitude and do not exceed the crowbar maximum.

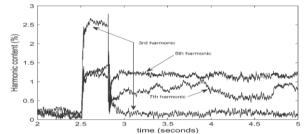

## B. THD Performance

Harmonic injection is a concern with STATCOMs [29]. A harmonic analysis has been performed on the output voltage at the point of common coupling. One of the primary reasons for using a multilevel converter is the reduction in harmonic content in the output waveform. Fig. 17 shows the harmonic distortion levels at the STATCOM PCC before, during, and after the fault. Since this is measured at the PCC, the output waveform has already been filtered to remove high-frequency components. Before the fault, the THD level is less than 1%, which is quite good. During the fault, the THD increases to over 5%. When the fault is removed, the THD decreases and settles at approximately 2.5%, which is in the acceptable range for a 115-kV system [30]. Therefore, the loss of one of the cells does not necessitate the immediate removal of the STATCOM from service. The increase in THD after removing the faulty cell is due to several reasons. First, the

#### International Journal of Modern Engineering Research (IJMER)

#### <u>www.ijmer.com</u> Vol.2, Issue.5, Sep-Oct. 2012 pp-3947-3955 ISSN: 2249-6645

STATCOM filters were tuned to the resonant frequencies associated with the eleven- level converter and are not as effective when the converter topology changes to a 9-level. Second, the over modulation required for the 9-level converter increases the content of the lower frequency harmonics. While the third harmonic is quite high during the fault, it returns to pre-fault levels after the fault is cleared, whereas the fifth and seventh remain fairly high due to the over modulation. Even though they are increased over the pre-fault value, they still remain under the 1.5%-limit required of 115-kV systems [30].

### V. EXPERIMENTAL RESULTS

To confirm the operation of the fault detection algorithm for cascaded H-bridge multilevel converters, an experimental prototype is constructed for applying and detecting different type of faults. The laboratory prototype of the STATCOM converter is shown in Fig. 18. The experimental rack consists of 36 Power ex CM75Du-24F IGBTs rated at 1200 V and 75 A for main switching devices. Passive components include a 1.2-mH, 45-A reactor and 18 electrolytic capacitors rated at 3900  $\mu$ F and 450 V. The IGBTs are driven by a Concept 6SD106E1 gate driver and controlled by a 320F2812 fixed-point digital signal processor (DSP).

For this prototype, three H-Bridge cells are cascaded to make a seven-level inverter for each phase of the STATCOM. During normal operation, the capacitor voltage for each cell is 30 V. A TMS320F2812 DSP is used for the calculation of the modulation, control, and fault detection algorithms. The H-bridges are constructed from the IGBTs switches and the gate signals of the IGBTs are delivered via fiber optic cables.

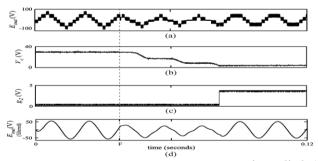

The output voltage of the converter during the normal operation, during the fault, and after removing the faulty cell is depicted in Fig. 19(a). A fault is applied to the second cell at point "F" as shown in the figure with the dashed line. Immediately after the fault is applied, the block capacitor begins to discharge. The capacitor voltage is shown in Fig. 19(b). Fig. 19(c) shows the output of the fault detection algorithm. When a fault is detected,  $g_2$  (the gate signal of the bypass circuit) becomes activated and it triggers the by-pass of the second cell and deactivates the PWM commands to the faulty H-bridge. Fig. 19(d) shows the filtered output of the STATCOM. Note that the amplitudes of the sinusoidal waveforms are nearly identical before and after fault detection and bypass. After detecting the fault and bypassing the faulty H-bridge, the modulation index is increased to compensate for the lost voltage levels in the output. In addition, the PWM switching patterns are modified based on existence of two cascaded H-bridges instead of three. This causes significant improvement in the output waveform of the converter.

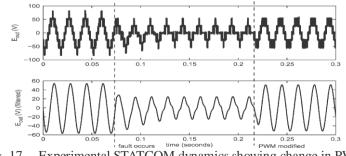

Fig. 20 shows the same fault as in Fig. 19, except the fault bypass signal is intentionally delayed by several cycles to demonstrate the effect of changing the PWM pattern. Note that after the fault and discharge of the corresponding capacitor, the output waveform contains considerable distortion. However, modifying the PWM switching signals based on two cascaded H-bridges, the THD of the output waveform can be significantly decreased and the filtered output waveform become sinusoidal again.

#### VI. CONCLUSION

In this paper, a fault allocation strategy for a multilevel cascaded converter has been proposed. This approach requires no extra sensors and only one additional bypass switch per module per phase. The approach has been validated on a 115-kV system with a STATCOM compensating an electric arc furnace load. This application was chosen since the arc furnace provides a severe application with its non-sinusoidal, unbalanced, and randomly fluctuating load. The proposed approach was able to accurately identify and remove the faulted module. In addition, the STATCOM was able to re- main in service and continue to provide compensation without exceeding the total harmonic distortion allowances.

Fig. 16. Experimental STATCOM dynamics before, during, and after a fault is applied; (a) *E*out , (b) capacitor voltage at faulted cell, (c) gating signal of cell 2 by-pass switch, and (d) *E*out (filtered).

Fig. 17. Experimental STATCOM dynamics showing change in PWM

### International Journal of Modern Engineering Research (IJMER)

www.ijmer.com Vol.2, Issue.5, Sep-Oct. 2012 pp-3947-3955 ISSN: 2249-6645

### REFERENCES

- [1] C.-H. Liu and Y.-Y. Hsu, "Design of a self-tuning PI controller for a STATCOM using particle swarm optimization," *IEEE Trans. Ind. Elec- tron.*, vol. 57, no. 2, pp. 702–715, Feb. 2010.

- [2] D. Soto and T. C. Green, "A comparison of high-power converter topologies for the implementation of FACTS controllers," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 1072–1080, Oct. 2002.

- [3] J. A. Barrena, L. Marroyo, M. Á. Rodríguez Vidal, and J. R. Torrealday Apraiz, "Individual voltage balancing strategy for PWM cascaded H-bridge converter-based STATCOM," *IEEE Trans. Ind. Electron.*, vol. 55, no. 1, pp. 21–29, Jan. 2008.

- [4] Y. Liu, A. Q. Huang, W. Song, S. Bhattacharya, and G. Tan, "Small- signal model-based control strategy for balancing individual DC capacitor voltages in cascade multilevel inverter-based STATCOM," *IEEE Trans. Ind. Electron.*, vol. 56, no. 6, pp. 2259–2269, Jun. 2009.

- [5] T. A. Meynard, M. Fadel, and N. Aouda, "Modeling of multilevel convert- ers," *IEEE Trans. Ind. Electron.*, vol. 44, no. 3, pp. 356–364, Jun. 1997.

- [6] C. Turpin, P. Baudesson, F. Richardeu, F. Forest, and T. A. Meynard, "Fault management of multicell converters," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 988–997, Oct. 2002.

- [7] S. Wei, B. Wu, F. Li, and X. Sun, "Control method for cascaded H-bridge multilevel inverter with faulty power cells," in *Proc. Appl. Power Electron. Conf. Expo.*, Feb. 2003, vol. 1, pp. 261–267.

- [8] S. Li and L. Xu, "Fault-tolerant operation of a 150 kW 3-level neutral point clamped PWM inverter in a flywheel energy storage system," in *Conf. Rec. 36th IEEE IAS Annu. Meeting*, Chicago, IL, Oct. 2001, pp. 585– 588.

- [9] B. McGrath and D. Holmes, "Multicarrier PWM strategies for multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 858–867, Aug. 2002.

- [10] J. I. Leon, S. Vazquez, S. Kouro, L. G. Franquelo, J. M. Carrasco, and J. Rodriguez, "Unidimensional modulation technique for cascaded multi- level converters," *IEEE Trans. Ind. Electron.*, vol. 56, no. 8, pp. 2981–2986, Aug. 2009.

- [11] P. Lezana, J. Rodriguez, R. Aguilera, and C. Silva, "Fault detection on multi cell converter based on output voltage frequency analysis," *IEEE Trans. Ind. Electron.*, vol. 56, no. 6, pp. 2275–2283, Jun. 2009.

- [12] Task Force on Harmonics Modeling and Simulation, "Modeling devices with nonlinear voltage-current characteristics for harmonic studies," *IEEE Trans. Power Del.*, vol. 19, no. 4, pp. 1802–1811, Oct. 2004.

- [13] F. Richardeau, P. Baudesson, and T. Meynard, "Failure-tolerance And remedial strategies of a PWM multicell inverter," *IEEE Trans. Power Electron.*, vol. 17, no. 6, pp. 905–912, Nov. 2002.

- [14] S. Khomfoi and L. Tolbert, "Fault diagnosis and reconfiguration for multilevel inverter drive using AI-based techniques," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2954–2968, Dec. 2007.

- [15] M. Ma, L. Hu, A. Chen, and X. He, "Reconfiguration of carrier-based modulation strategy for fault tolerant multilevel inverters," *IEEE Trans. Power Electron.*, vol. 22, no. 5, pp. 2050–2060, Sep. 2007.

- [16] S. Ceballos, J. Pou, E. Robles, I. Gabiola, J. Zaragoza, J. L. Villate, and D. Boroyevich, "Three-level converter topologies with switch breakdown fault-tolerance capability," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 982– 995, Mar. 2008.

- [17] P. Barriuso, J. Dixon, P. Flores, and L. Morán, "Fault-tolerant reconfig- uration system for asymmetric multilevel converters using bidirectional power switches," *IEEE Trans. Ind. Electron.*, vol. 56, no. 4, pp. 1300– 1306, Apr. 2009.

- [18] P. Lezana and G. Ortiz, "Extended operation of cascade multicell con-verters under fault condition," *IEEE Trans. Ind. Electron.*, vol. 56, no. 7, pp. 2697–2703, Jul. 2009.

- [19] F. Z. Peng, J. S. Lai, W. McKeever, and J. VanCoevering, "A multilevel voltage source inverter with separate dc sources for static VAr generation," *IEEE Trans. Ind. Appl.*, vol. 32, no. 5, pp. 1130–1138, Sep. 1996.

#### **About Authors**

**B. Bansiraj** was born in 1985. He Received B.Tech (Electrical & Electronics Engineering) degree from Jawaharlal Nehru Technological University college of engineering, Kakinada, A.P., India in 2006. He has 4 years teaching experience in various engineering colleges in India. Presently He is Pursuing M.Tech (Power Electro-nics & Electrical Drives) from Mother Teresa Institute of Science & Technology, Sathupally, India affiliated by JNTU Hyderabad, India. His area of interest is Power Electronics, Power System.

**Mr.M.LOKYA** was born in 1984. He graduated from KAKATIYA UNIVERSITY, in the year 2005. He received M.Tech degree from Jawaharlal Nehru Technological University, Hyderabad in the year 2011. He is presently working as Assistant Professor in the Department of Electrical and Electronics Engineering at Mother Teresa Institute of Science and Technology, Andhra Pradesh, India.