# **On Chip Bus Tracer Based On Reverse Encoding In Soc**

# Blessy Babu<sup>1</sup>, Karthika Manilal<sup>2</sup>

<sup>1</sup>PG Scholar, Dept. of Electronics and Communication Engg, TKM Institute of Technology, Kollam, Kerala, India <sup>2</sup>Asst.Professor, Dept. of Electronics and Communication Engg, TKM Institute of Technology, Kollam, Kerala, India

**Abstract:** System on chip (SoC) is the integration of different components in to a single chip targeting a specific application. Real-time observability of the internal chip signals is crucial to SoC debugging, the obvious choice would be to use chip pins to observe them. However, this method is difficult to implement in the presence of high frequency internal clocks and limitation of the chip pins. A solution to this problem is to embed a bus tracer in SoC to capture bus signal, and to store the trace in on-chip storage (trace memory). The size of bus trace increases rapidly as the numbers of transactions are more. In order to reduce the trace size, compression is necessary. These compression algorithms use forward encoding method i.e. first data is recorded as uncompressed and all others are encoded. Trace memory is a circular buffer, so in case of wrapping around this may result in loss of data and affects the decompression flow. Therefore a new reverse encoding method is used that results in efficient circular buffer utilization. To capture the bus signals, an on-chip communication architecture based on WISHBONE bus, with four masters and four slaves is designed and the hardware tracer based on reverse encoding is integrated to this. This is coded using VHDL, simulated using ModelSim 6.4c and synthesized using Xilinx ISE tool.

## I. INTRODUCTION

The growing complexity and shorter time to market constraint makes verification and debugging a major hurdle in shortening development cycle of system on chip.

In contrast to software debugging, hardware debugging methods provides insight to observability of internal state system and real time behavior in SoC. The limitation of this approach is unavailability of dedicated pins and increased gap of internal and external frequencies while moving trace out of chip. This leads to demand for on chip debugging units. The main problem dealing with the on chip debug units is that execution trace in SoC is large and hence for storing these much data results in increased cost of hardware implementation and data acquisition systems. The solution to this problem is to integrate a tracer in to the bus, which is the communication architecture in SoC, to capture and compress signal in real time and store them in an on-chip trace memory. The traced data can then be decompressed on the software terminal for performance analysis, bus utilization and verification.

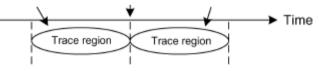

Trace collection is controlled by user defined signal condition. They are two types of traces forward trace and backward trace. As shown in figure 1 the forward/backward trace refers to trace captured before/after a triggering event. The forward trace is used for diagnosing errors at known time periods and backward trace is used for detecting the system Backward trace Event trigger Forward trace

Fig.1. Difference between forward trace and backward trace

| Time                                 | <br>t+4    | t+5   | t+6            | t+7               | t+8   |

|--------------------------------------|------------|-------|----------------|-------------------|-------|

| Input data                           | <br>0x844  | 0x848 | 0x850<br>Trace | 0x830<br>capacity | 0x834 |

| Traditional<br>encoding<br>algorithm | <br>0x844∢ | + 0x4 | + 0x8          | - 0x20            | + 0x4 |

Fig.2. forward encoding differential compression algorithm malfunctioning.

Traces which are collected are stored in a trace memory; since capacity is limited it is usually used as circular buffer. In case of backward trace, signals are continuously collected, so when trace memory is full, wrapping around occurs i.e., initial data become overwritten. This causes a problem when the trace needs to be compressed.

For example, Fig.2 shows traditional differential compression algorithm that make use of forward encoding. It works as follows. First datum is recorded as uncompressed; when second datum comes it is encoded with respect to first, ie, difference between the first and second is stored. When third datum comes it is encoded with respect to second and so on. The problem occurs when first data become overwritten due to wrapping around in circular buffer. This initial data is in uncompressed format and all other dates are encoded with respect to that .Therefore when it is lost all other data's becomes useless ie, they cannot be decompressed.

In this paper a reverse encoding algorithm is proposed. This algorithm is applied to different popular compression algorithms and demonstrated in an on WISHBONE bus for SoC. The tracer supports both forward and backward trace with effective circular buffer utilization in addition to good compression ratios and small hardware overhead.

This paper is organized as follows. Section II discusses related work regarding tracers. Section III presents the proposed algorithm. Section IV introduces architecture of on chip bus tracer. In Section VI, the experimental results a are discussed. Section VIII concludes this paper.

# **II. RELATED WORKS**

The execution traces in SoC is large so there needs a large amount of memory for storing these data's .This results the need of reduction/compression techniques. They techniques are divided into lossy and lossless approaches.

Lossy approach has the advantage of high compression ratio [3]. The idea is to capture only the erroneous signals in a trace buffer to increase the trace-buffer utilization. Here a three pass methodology is used. During the first pass, the rough error rate is measured, in the second pass, a set of suspect clock cycles where errors may be present is determined, and then in the third pass, the trace buffer captures only during the suspect clock cycles. In this manner, the effective observation window of the trace buffer can be expanded significantly, by up to orders of magnitude. This greatly increases the effectiveness of a given size trace buffer and can rapidly speed up the debug process.. But it is not suitable for real time on chip bus tracing

Lossless data compression algorithms can be classified into two main categories statistical coding algorithms and dictionary coding algorithms [5] Statistical based compression algorithms, such as Huffman coding or arithmetic coding can lead to an optimal average code length and hence good compression ratio. For the real-time requirement and the fact that debug data is not known a-priori these static methods are not suitable. The second category of data compression algorithms is the dictionary-based compression algorithms. The compression in these methods is achieved by encoding a symbol or a sequence of consecutive symbols into shorter code words which are represented by indices to the dictionary locations. But this approaches face difficulty when wrapping around occurs because they use forward encoding algorithm.

For effective debugging they must support both forward and backward trace .The logic analyzers [7] support forward trace but they have no compression ability and backward trace capability.

In ARM ETM [6] and NEXUS interface, data filtering is used to increase trace depth. They use a branch target technique to compress instruction address: it ignores consecutive address and stores only branch and target address. The hardware overhead of these works is small since

the filtering mechanism is simple to implement in hardware. However, the effectiveness of these techniques is mainly limited by the average basic block size, which is roughly around four or five instructions per basic block,

Periodical triggering supports both forward and backward trace[4].Here trace memory is divided into small segments using a ping pong organization. These segments are compressed separately hence destruction of one segment does not affect another. But has a disadvantage of more uncompressed data. Utilization ratio can be increased by increasing the segments but it reduces the compression ratio.

# III. REVERSE ENCODING ALGORITHM

To overcome the disadvantage of data loss due to wrapping around in circular buffer a reverse encoding is applied to different compression algorithms in trace reduction stage. In this newest data is set to uncompressed and all other preceding datum's are encoded with respect to the newest so when first data is removed, it doesn't affect the decompression because it is only a encoded value not the initial uncompressed data. As in reverse encoding, there is a difference from Fig.2.i.e.0x834 is set as uncompressed and all others are encoded with respect to that.

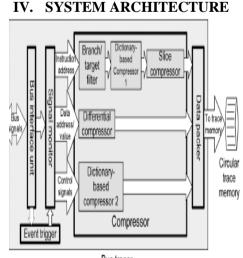

## Bus tracer Fig.3.Bus tracer hardware architecture

#### International Journal of Modern Engineering Research (IJMER) www.ijmer.com Vol.3, Issue.1, Jan-Feb. 2013 pp-317-323 ISSN: 2249-6645

Fig. 3 shows the hardware architecture of the bus tracer. It has two major functional modules (1) signal monitor /tracing and (2) trace compression. Signal monitor consist of event trigger, bus interface unit and signal monitor. Bus interface unit handles bus requests and collects the bus signal for storing, signal monitor synchronizes the signals and pass these signals to data reduction stage, where reverse encoding is applied. Event trigger module is configurable and controls trigger condition of start/stop a trace. When triggered the bus tracer starts capturing signals and stops until another trigger happens. Finally, the data packer packs the compressed data and writes them to the circular trace memory.

As shown in Fig. 3 bus signals are classified into three, instruction address, data address/value, and control signals. Instruction addresses are processed in three steps. First is to record only the non sequential jumping address. In virtual of the computer program usually having the property of spatial locality, each adjacent address pattern often is increased by a sequential offset. Hence, we can choose to only record the adjacent address pattern increased by a non-sequential offset, also called branch jump address, so as to eliminate the most address information. Secondly such branch/target addresses repeat addresses. Third, the higher part between two adjacent address patterns is almost similar. Hence, if we can make the similarity between the current address and the previous address to be eliminated, the compression ratio may be rising dramatically. So the dictionary-based compressor 2 (shown in Fig. 3). Because the variety of transfer types in a system is usually small, the same transfer types appear frequently. Therefore, the control signal patterns indicating the transfer types also appear frequently, which enables the dictionary-based method to reduce the size of the repeated signal patterns. The signal variations on data bus (data address and data value buses) are not regular that compared with program address bus. Using the differential approach based on subtraction is the convenience way to reduce the data bus trace size and the hardware cost of subtraction module is small.

The following sections show how to apply our reverse-encoding algorithm to the compression methods used in this bus tracer

#### A. Differential Compression

Compared to forward encoding, reverse encoding differ in following areas (1) since forward encoding records the first datum as uncompressed while reverse encoding records last datum as uncompressed (2) forward encoding relates the present datum to the previous datum while the reverse encoding relates the present datum to the next datum. The encoded results of both forward and reverse encoding are same because absolute difference is not changed after interchanging the minuend and the subtrahend.

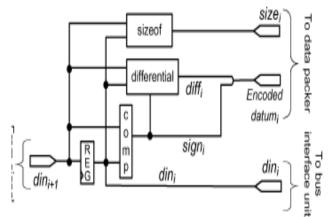

Fig. 4. Differential compressor hardware based on reverse encoding

Fig. 4 shows the differential compressor hardware based on reverse encoding. The present datum is represented as dini and next datum is represented as dini+1, dini+1 is obtained by delaying the input data with a register *REG*. For each cycle three outputs are generated: 1) the absolute difference, which is obtained by subtracting the present datum from the next datum; 2) the sign magnitude, which is obtained by comparing the two data, that results in identifying whether the result is positive or negative; and 3) *sizei*) which indicates the number of meaningful bits of the difference. The reason for representing the difference as the absolute value and a signed magnitude is because the high-order bits of the absolute difference are usually zeros and can be discarded. The absolute difference and the sign magnitude are further packed together to form the final encoded datum. Finally, the data packer module stores the meaningful low-order bits of the encoded datum according to the size. In addition, to record the last datum in uncompressed format, we can read it from the register *REG* when the trace stops. Therefore, the register *REG* is implemented as the interface register of the tracer so that it can access via the bus.

#### **B. Slice Compression**

The basic principle of slice compression is that the higher parts between two adjacent branch/target address data are almost similar. Hence, by the elimination of the similar parts, the compression ratio can be raised. Table I shows an example of forward-/reverse-encoding slice compression for a set of instruction addresses. In the forward encoding, the first address is kept uncompressed. The succeeding address is encoded as its differential bits from the preceding address, .eg., 0x0300\_6120 is encoded as 0x120 since the difference between 0x0300\_6120 and 0x0300\_6600 is 0x120. For reverse encoding, the reference direction is reversed; the last address is kept uncompressed while the previous ones are encoded based on the uncompressed last address.

| Time | Original    | Forward     | Reverse     |

|------|-------------|-------------|-------------|

|      | address     | encoding    | encoding    |

| t    | 0x0300_6600 | 0x0300_6600 | 0x600       |

| t+1  | 0x0300_6120 | 0x120       | 0x20        |

| t+2  | 0x0300_6130 | 0x30        | 0x300_6130  |

| t+3  | 0x0080_4020 | 0x080_4020  | 0x020       |

| t+4  | 0x0080_4400 | 0x400       | 0x0080_4400 |

Table I Example of slice compression for forward/reverse encoding

The implementation of the reverse-encoding slice compression is similar to that of the differential compression, as shown in Fig. 4. The only difference is that the *sizeof*, *differential*, and *comp* modules now compare the bit difference of two data.

#### **C. Dictionary-Based Compression**

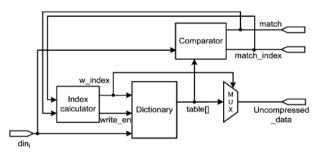

Fig.5. Dictionary compressor hardware based on forward encoding

In dictionary based compression the idea is to map the data to a table keeping frequently appeared data, and record the table index instead of the data to reduce size. Fig. 5 shows the hardware architecture of forward encoding dictionary compression. For each input datum, the comparator compares the datum with the data in the dictionary. If the datum is not in the table (Match=Miss), the datum is written into the table and also recorded in a trace. Otherwise, the index of the hit table entry (Match=Hit) is recorded instead of the datum. But the problem associated with this is that when wrapping around occurs, the uncompressed datum might be overwritten, resulting in data loss. Consider a example that we are sending a series of data's a1, a2, a3, a4, a5, a6.a1 to a3 has the same value as do a4 to a6. At first cycle, since the table is empty, input datum does not match with any table entry (known as a Miss). Therefore, it is inserted into the table and immediately recorded in an uncompressed format. At second and third cycle, a2 and a3 are the same; hence they are encoded as the indexes, respectively. At fourth clock cycle, a4 replaces a1 becausea4 is different from a1 (known as a Miss) and the table has only one entry, replaces. In this encoding algorithm, when a1 is overwritten, a2 and a3 cannot be decompressed.

Reverse encoding based dictionary compression can eliminate this problem. Concept of reverse encoding is that, the recording of a1 is delayed: It is only recorded until it is replaced with a4. As a result, the encoded data are placed before the uncompressed datum .With this order, the wrapping around does not cause data loss since the encoded data are lost before the related uncompressed data.

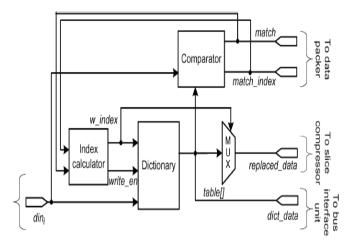

Fig.6. shows the dictionary-based compressor hardware based on reverse encoding. The input datum is compared with the data in the dictionary (din1) by the comparator. If there is a match, then the comparator sends the matched entry number (match index) to the data packer. If not, the input datum is inserted in the dictionary according to the index (w\_index) calculated by the index calculator. At the same time, the replaced datum (replaced data) is output to the slice compressor for the further processing.

Fig.6. Dictionary compressor hardware based on reverse encoding

Main difference between forward and reverse encoding is that when data's are placed in dictionary they are not immediately recorded, it is recorded only when the data's are replaced.

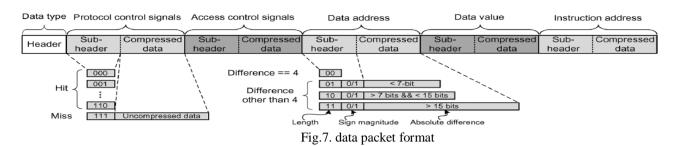

# V. DATA PACKER

Data packer receives the compressed data from the compression module, processes them, and writes them to the circular trace memory. It is responsible for: packet management and circular buffer management. For packet management, since the compressed data length and type are variable, every compressed data needs a header for interpretation. Therefore, this step generates a proper header and attaches it to each compressed datum. Fig.7 shows data packet example. Last packet contains the uncompressed date hence decompression starts from this. since the decompression works in a backward order, in order to interpret the content of a packet, the header is placed at the end of a packet so that the header can be read first before the trace data. It is obtained by reversing the bit order of a packet, since the sub headers should also be read before the compressed data.

#### VI. SIMULATION RESULTS

As an experimental study a communication architecture based on wishbone in SoC is designed consisting of four masters and four slaves .Master 1 is designed as processor and slaves as memories and the bus tracer based on reverse encoding is integrated to this architecture for tracing the processors program memory. Fig.8, Fig.9, Fig.10 shows results of master 1 communication to external memory

Fig.8.Simulation result of master 1 during write operation

| ) /icn002/cyc_o_m0 | 1                 |      |         |        |  |       |            |       |  |

|--------------------|-------------------|------|---------|--------|--|-------|------------|-------|--|

| /icn002/gntmux     | 00                | 00   |         |        |  |       |            |       |  |

| /icn002/dat_o_m0   | 00000000000000100 |      | 0000010 | 10     |  | (0000 | 0000000    | 00    |  |

| /icn002/stb_o_m0   | 1                 |      |         |        |  |       |            |       |  |

| /icn002/adr_o_m0   | 01010             | 000  |         |        |  | (0010 |            | 01010 |  |

| /icn002/we_o_m0    | 1                 |      |         |        |  |       |            |       |  |

| /icn002/ist        | 0                 |      |         |        |  |       |            |       |  |

| /icn002/ck         | 1                 |      |         |        |  |       |            |       |  |

| /icn002/acmp1      | 1                 |      |         |        |  |       |            |       |  |

| /icn002/stb_i_s1   | 1                 |      |         |        |  |       |            |       |  |

| /icn002/dat_o_s0   | 00000000000000    | UUUU | JUUUUUU | 000000 |  |       |            |       |  |

| /icn002/dat_o_s1   | υυυυυυυυυυ        | UUUL | JUUUUUU | UUUUUU |  |       |            |       |  |

| /icn002/dat_o_s2   | 0000000000000     | UUUL | JUUUUUU | UUUUUU |  |       |            |       |  |

| /icn002/dat_o_s3   | υυυυυυυυυυ        |      |         |        |  |       |            |       |  |

| /icn002/drd        | υυυυυυυυυυ        | UUUL | JUUUUUU | UUUUUU |  |       |            |       |  |

|                    | 01010             | w    |         |        |  | (0010 |            | 01010 |  |

| > /icn002/dwr      | 00000000000000100 |      | 0000010 | 10     |  | (0000 | 0000000101 | 00    |  |

| > /icn002/we       | 1                 |      |         |        |  |       |            |       |  |

| 👌 /icn002/stb      | 1                 |      |         |        |  |       |            |       |  |

| /icn002/ack        | 1                 |      |         |        |  |       |            |       |  |

| /icn002/ack_i_m0   | 1                 |      |         |        |  |       |            |       |  |

Fig.9. Simulation result of wishbone bus during write operation

The bus tracers traces both the communication, read and write to the external memory and compresses these using reverse encoding compression algorithms and stores them in circular trace memory. This is shown in Fig.11

| /icn002/u11/ack_o  | U                                       |       |           |      |     |          |         |         |       |           |         |          |

|--------------------|-----------------------------------------|-------|-----------|------|-----|----------|---------|---------|-------|-----------|---------|----------|

| /icn002/u11/adr_i  | 001                                     | 1001  |           |      |     |          |         |         | (100  |           | 010     |          |

| /icn002/u11/clk_i  | 1                                       |       |           |      | ٦   |          |         |         |       |           |         |          |

| /icn002/u11/dat_i  | 0000000000010110                        | 10000 | 000000010 | 110  |     |          |         |         | )0000 | 000000000 | 00      |          |

| /icn002/u11/stb_i  | 1                                       |       |           |      |     |          |         |         |       |           |         |          |

| /icn002/u11/cyc_i  | 1                                       |       |           |      |     |          |         |         |       |           |         |          |

| /icn002/u11/we_i   | 1                                       |       |           |      |     |          |         |         |       |           |         |          |

| /icn002/u11/arrmem | (00000000000000000000000000000000000000 | {UUL  | υυυυυυι   | JUU  | JUU | ((000000 | 0000000 | 0000000 | 00000 | (000000   | 0000000 | <u> </u> |

| (7)                | υυυυυυυυυυ                              | UUU   | ύυυυυυυ   | ψυι  | UUU |          |         |         |       |           |         |          |

| > (6)              | 000000000000000000000000000000000000000 | UUU   | ύυυυυυυ   | ψυι  | UUU |          |         |         |       |           |         |          |

| > (5)              | 000000000000000000000000000000000000000 | UUU   | ύυυυυυ    | υυι  | UUU |          |         |         |       |           |         |          |

| > (4)              | υυυυυυυυυυ                              | UUU   | ύυυυυυυ   | ύυι  | UUU |          |         |         |       | 000000000 | 0000100 |          |

| > (3)              | 000000000000000000000000000000000000000 | UUU   | ύυυυυυυ   | υυι  | UUU |          |         |         |       |           |         |          |

| > (2)              | υυυυυυυυυυ                              | UUU   | υυυυυυ    | υυι  | UUU |          |         |         |       |           |         |          |

| <b>&gt;</b> m      | υυυυυυυυυυ                              | UUU   | ύυυυυυ    | ίυυι | UUU |          | 0010110 |         |       |           |         |          |

| (0)                | 000000000000000000000000000000000000000 | UUU   | υυυυυυ    | υυι  | UUU |          |         |         |       |           |         |          |

| /icn002/u12/ack_o  | U                                       |       |           |      |     |          |         |         |       |           |         |          |

Fig.10. Simulation result external memory during write operation

The decompression is shown in Fig.12 which includes packet de-assemble and decompression of all these compression algorithms

|                            | -                    |             |            | _         |          |           |           |            |                |            |         |             |             |               |             |             | _     |

|----------------------------|----------------------|-------------|------------|-----------|----------|-----------|-----------|------------|----------------|------------|---------|-------------|-------------|---------------|-------------|-------------|-------|

| /pack_al/buff/overflow     | U                    |             |            |           |          |           |           |            | _              |            |         |             |             |               |             |             |       |

| 🔶 /pack_al/buff/buffere    |                      |             |            |           |          |           |           |            |                |            |         |             |             |               |             |             |       |

| /pack_al/buff/bufer        |                      | {-21474836- | 48-214     | 11)11(11  | DUQ1     | 11 (33 10 | 447} {-56 | 16 479}    | {15 18         | 496} {13   | 11510}  | 43 14 4     | 27} {-      | 13 490}       | 5 10 462}   | 49 487}     | -578  |

| /pack_all/buff/front       | 21                   | 1           |            | 11)11(11  | 10001    | )))21     |           |            |                |            |         |             |             |               |             |             |       |

| /pack_all/buff/rear        | 21                   | 1           |            | 12        | 3 )4     | 5 6       | 17 18     | 9 10       | ) <u>m h</u> z | (13 )14    | 15 16   | (17 )18     | (19.)       | 0 (21         |             |             |       |

| /pack_all/packet_assde     |                      |             |            |           |          | ulonu     |           | li ta bi   | I MINI         |            |         |             |             |               |             |             |       |

| /pack_all/packet_assde     |                      |             |            |           |          |           |           |            |                |            |         |             |             |               |             |             |       |

| /pack_all/packet_assde     | 10 2 100             | 214748364   | 8 -214748  | 648(      | 1        |           |           | į          |                | (1)        | 5       | ()          | 1           | (10.2         | 00          |             |       |

| /pack_all/packet_assde     |                      |             |            |           |          |           |           |            |                |            |         |             |             |               |             |             |       |

| /pack_all/packet_assde     | 33 -66 15 18 43 -4 5 | -214748364  | 8 -214748  | 3648(     |          |           | .) 3      | X 3        | ГT             | (3)        | 3       | (3)         | 3           | 33-6          | 5 15 18 43  | 45-4-57     | 2 31  |

| /pack_all/packet_assde     | 10 15 18 11 14 13 1  | 214748864   | 8 -214748  | 3648(     | 1        |           | .) ]1     | ( <b>1</b> |                | (1)        | 1       | (1)         | 1           | (10 16        | 18 11 14 1  | 3 10 9 8 19 | 20 1  |

| /pack_all/packet_assde     | 447 479 498 510 42   | 2114748864  | 8 -214748  | 648(      | 104      |           | .) ]4     | ( <b>4</b> |                | [4]        | 4]      | (4)         | (4)         | (447.4        | 79 498 510  | 427 490 4   | 248   |

| /pack_all/decoder_diff/dk  |                      |             |            | n mi      | Think    | TIT       | TH TH     |            | THTT:          |            |         | TT TH       |             | 1 Million     |             |             | TIN   |

| /pack_all/decoder_diff/en  |                      |             |            |           |          |           |           |            |                |            |         |             |             |               |             |             |       |

| /pack_all/decoder_diff/    | 33 -66 15 18 43 -4 9 | -214748364  | 8 -2147483 | 3648      | 13       | 3.        | 1 3       | I 3        | П              | [3]        | 31      | [3]         | <u>1</u> 31 | <u>[</u> 33-6 | 15 18 43    | 45-4-57     | 12 31 |

| /pack_all/decoder_diff/    | 10 20 35 65 45 12 1  | 214743354   | 8 -214748  | 3648-214  | 7483348  | -2147483  | 648 -2147 | 483648 -   | 214748         | 3648 -21-  | 748354  | -21474      | 864         | 2110 2        | 35 65 45    | 12 17 18 19 | 50 6  |

| /pack_all/decoder_dict/ck  |                      | THEFT       |            | 1.1110    | 1000     | T TTT     | 10 011    |            | I IIII         |            |         |             | [[]]        |               |             |             | TIN   |

| /pack_all/decoder_dict/    | -2147483648 -2147    | III         | ()))) ([-2 | 14748364  | 8 -21474 | 83648 -2  | 47483648  | -214748    | 3648 -2        | 14748364   | 8 -2147 | 83648 -     | 214748      | 3648 15       | 18 14 13 10 | 981654      | 32    |

| /pack_all/decoder_dict/    | 10 16 18 11 14 13 1  | 78147/43834 | 8 -214748  | 3648(     | 1 1      | . 1       | 1 h.      | Î 1.       | 11             | <b>1</b> 1 | 11      | <u>(i</u> ] | 1.1         | ĺ10 16        | 18 11 14 1  | 3 10 9 8 19 | 20 1  |

| /pack all/decoder_dict/    | 1001000001101011     | ILLUDING .  | 111110     | 00100000  | 1101011  | 000       |           |            | -              |            |         |             |             | <u> </u>      |             |             |       |

| /pack_all/decoder_dict/    | 23454465123          | -214748364  | 8 -2147483 | 3648 -214 | 7483648  | -2147483  | 648 -2147 | 483648     | -214748        | 3648 - 21- | 748364  | -21474      | 33648       | 2234          | 544651      | 238910      | 13 14 |

| /pack_all/decoder_dict/fin |                      |             |            |           |          |           |           |            |                |            |         |             |             |               |             |             |       |

| /pack_all/decoder_dict/    | (uuuuu) (uu          |             | Huuu       | uu) {uu   | taaa     | ) tuuu    | uul} {uu  | uuuu       | Yauu           | uuu}{      | iuuu    | u) {uu      | uuu         | }{uu          | uuus (u     | uuut)       | uu    |

| /pack_all/decode_sice/dk   |                      |             |            |           | 1 mini   | TITT      | TT ITT    |            | TUTT.          |            |         | TT TT       |             |               |             |             | TIN   |

| /pack_all/decode_slice/    |                      |             |            |           |          |           |           |            |                |            |         |             |             | Γ             |             |             |       |

| /pack_all/decode_slice/    | 447 479 498 510 42   | -214743364  | 8 -2147483 | 648[      | 104      |           | 1 H       | í 4        | 11             | [4]        | 4]      | [4]         | [4]         | (447.4        | 79 498 510  | 427 490 48  | 2 48  |

| /pack all/decode sice/     | 100 200 150 400 23   | 214748664   | 8 -214748  | 3648 -214 |          |           | 648 -2147 | 483648     | 214748         | 3648 -21   | 748364  | -21474      | 8648        | 2147)         |             | (())))(((   | 100 2 |

| hade all decode deal       | 100 200 150 400 23   |             |            |           |          |           |           |            |                |            |         |             |             |               |             | 1000        |       |

Fig.11.simulation results of reverse encoding compression algorithms

| /padk_al/dkt1/dk 1                      |                                                                                                                                                                           |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ▶ /pack_al/ckt1/diff_trace 33 -66 15 18 | 143 - 45 <mark>33 - 66 15 18 43 - 45 - 4 - 57 12 31 1 1 5 - 33 -</mark> 20 30 15 10 10                                                                                    |

| /pack_al/dkt1/a -214748364              | -2147483648                                                                                                                                                               |

|                                         | 45 12 11 10 20 35 65 45 12 17 18 19 50 62 5 1 6 2 45 63 78 12 45                                                                                                          |

| \land /pack_all/trans/ck 1              |                                                                                                                                                                           |

| 🔶 /pack_al/trans/fin 🛛 1                |                                                                                                                                                                           |

|                                         | 14 13 11 <mark>000000000000000000000000000000000</mark>                                                                                                                   |

| -214748364 -214748364                   | 8 -21474 <mark>100 11 100 11 11 12 11 147433648 -2147483648 -2147483648 -2147483648 -2147483648 -2147483648 -2147483648 -2147483648 16 18 14 13 10 9 8 1 6 5 4 3 2</mark> |

|                                         | 1010111/ <mark>10101010101010101010000110100000</mark>                                                                                                                    |

| -214748364                              | 8 -21474 11(1 ) (1 ))))))))))))))))))))))))))))                                                                                                                           |

|                                         | 5123 234544651238910131413181614                                                                                                                                          |

| /pack_al/sice_tx/ck 1                   |                                                                                                                                                                           |

| /pack_al/slice_tx/comp 1                |                                                                                                                                                                           |

|                                         | 510 42 11(1)))11(1))11(1)(447 479 498 510 427 490 462 487 508 434 401 444 432 464 389 445 426 58 172 100                                                                  |

|                                         | 400 23 100 200 150 400 23 55 85 96 12 45 35 78 27 41 36 65 85 12 45 96                                                                                                    |

| /pack_al/packet/dk 1                    |                                                                                                                                                                           |

| 🔶 /pack_al/packet/en 1                  |                                                                                                                                                                           |

|                                         | 143 - 45 <mark>33 - 66 15 18 43 - 45 - 4 - 57 12 31 1 1 5 - 33 -</mark> 20 30 15 10 10                                                                                    |

|                                         | 14 13 11 <mark>1111111111111111111111111111111</mark>                                                                                                                     |

|                                         | 510 42 0111111111111111111111111111111111                                                                                                                                 |

| 🖂 /pack_all/packet/packe 10 2 100       | -2147483648 -2147 0000000000000000000000000000000000                                                                                                                      |

| 🔶 /pack_al/buff/putck 🛛 0               |                                                                                                                                                                           |

| /pack_al/buff/getck 1                   |                                                                                                                                                                           |

| A                                       |                                                                                                                                                                           |

Fig.12.Simulation results of decompression of algorithms

The whole architecture is modeled using VHDL. Simulation was done using Modelsim XE III 6.4 and is synthesized using Xilinx ISE 9.2i

## V. CONCLUSION

During design implementation stage and final chip testing bus signal tracing (bus tracer) can help designer to debug and analyze hardware-software design. Traditional tracers use forward-encoding compression algorithms to reduce the data size. However, such algorithms are not suitable for a backward trace with a circular buffer. So a reverse encoding based bus tracer is proposed that support both forward and backward trace. This tracer is integrated on wishbone bus consisting of four masters and four slaves. The result shows that this tracer can achieve good circular buffer utilization.

#### REFERENCES

- [1] Fu-Ching Yang, "Reverse encoding based on chip bus tracer for effective circular buffer utilization", IEEE Trans. vlsi, vol. 18, no. 50, pp. 732–739, 2010.

- [2] Ayas kantha swain," Design and verification of wishbone bus interface for system on chip integration", 2010 annual IEEE India conference

- [3] J.-S. Yang and N. A. Touba, "Expanding trace buffer observation window for in-system silicon debug through selective capture," in Proc. IEEE 26th VLSI Test Symp., Apr. 27–May 1 2008, pp. 345–351.

- [4] Y.-T. Lin, W.-C. Shiue, and I.-J. Huang, "A multi-resolution AHB bus tracer for read-time compression of forward/backward traces in a circular buffer," in Proc. DAC, Jul. 2008, pp. 862–865.

- [5] E. Anis and N. Nicolici, "On using lossless compression of debug data in embedded logic analysis," in Proc. IEEE Int. Test Conf., Oct. 2007, pp. 1–10.

- [6] ARM, Ltd., Cambridge, U.K., "Embedded trace macrocell architecture specification," 2002. [Online]. Available: <u>http://infocenter.arm.com/</u>

- [7] Altera Corporation, San Jose, CA, "Signal Tap embedded logic analyzer mega function," 2001. [Online]. Available: http://www.altera.com/literature/ ds/dssignal.pdf