| IJMER | ISSN: 2249–6645 |

# Design and Implementation of 8 Bit Multiplier Using M.G.D.I. Technique

## Nitin Singh<sup>1</sup>, M. Zahid Alam<sup>2</sup>

<sup>1</sup>Dept. of Electronics & Communication Engineering Lakshmi Narain College of Technology, Bhopal <sup>2</sup>Dept. of Electronics & Communication Engineering Lakshmi Narain College of Technology, Bhopal

Abstract: In this paper we have implemented Radix 8 High Speed Low Power Binary Multiplier using Modified Gate Diffusion Input(M.G.D.I) technique. Here we have used "Urdhva-tiryakbhyam" (Vertically and crosswise) Algorithm because as compared to other multiplication algorithms it shows less computation and less complexity since it reduces the total number of partial products to half of it. This multiplier at gate level can be design using any technique such as CMOS, PTL and TG but design with new MGDI technique gives far better result in terms of area, switching delay and power dissipation. The radix 8 High Speed Low Power Pipelined Multiplier is designed with MGDI technique in DSCH 3.5 and layout generated in Microwind tool. The Simulation is done using 0.12µm technology at 1.2 v supply voltage and results are compared with conventional CMOS technique. Simulation result shows great improvement in terms of area, switching delay and power dissipation.

Keywords: Adder, CMOS, MGDI, Multiplier, Power Dissipation, Ripple Carry Adder

#### I. INTRODUCTION

The majority of the real life applications mainly in microprocessors and digital signal processors require the computation of the multiplication operation [1]. Specifically speed, area and power efficient implementation of a multiplier is a very challenging problem. Multipliers are the main building block of many high speed and performance systems such as FIR filters, microprocessors, and digital signal processors. The performance of digital system is generally evaluated by the performance of the multiplier. In such applications, low power consumption is also a critical design issue.

Power dissipation in CMOS circuits [2] is caused by three main sources: 1) the charging and discharging of capacitive loads due to change in input logic levels. 2) the short-circuit current arises because of the direct current path between the supply rails during output transitions and 3) the leakage current which is determined by the fabrication technology, consist reverse bias current in the parasitic diodes formed between source and drain diffusions and the bulk region in a transistor as well as the sub threshold current that arises from the inversion charge that exists at the gate voltages below the threshold voltage, The short- circuit and leakage currents in CMOS circuits can be made small with proper device and circuit design techniques. The dominant source of power consumption is the charging- discharging of the node capacitances and it can be minimizing by reducing switching activity of transistors. Switching activity of the digital circuits is also a function of the logic style used to implement the circuit. At circuit/logic level [2], different CMOS logic design techniques like CMOS complementary logic, Pass Transistor Logic, Pseudo nMOS, Cascade voltage switch logic , Dynamic CMOS, Clocked CMOS logic , CMOS Domino logic, Modified Domino logic and transmission gate logic (TG) have been proposed to reduce power consumption. The new MGDI technique called modified gate diffusion input technique allows solving most of the problems occurring in above mentioned various CMOS and PTL techniques. The MGDI technique compared to other techniques allows reduced power dissipation, lower time delay, lower count of transistors and area of digital circuits while maintaining reduced complexity of circuit logic.

In this paper, we designed low power, fast processing radix 4 Pipelined Multiplier for 2, 4 and 8 bit multiplication using MGDI technique that has advantages of minimum transistors required, more speed and low power dissipation as compare to conventional CMOS techniques. The organization of this paper is as follows: Section II, explains the details of "Urdhva-Tiryakbhyam" i.e. vertically and crosswise Multiplication Algorithm for 2 bit ,4 bit and 8 bit Multiplication.. Section III, explains MGDI technique and its performance analysis for basic digital gates. Section IV, presents the implementation of radix-4 Pipelined multiplier using MGDI in DSCH 3.5 and MICROWIND Tool. At the end, the conclusion and Acknowledgement is presented in section V & VI.

#### II. VEDIC MULTIPLICATION ALGORITHM

The multiplier is based on an algorithm called Urdhva Tiryakbhyam (Vertical & Crosswise) of ancient Indian Vedic Mathematics [4]. Urdhva Tiryakbhyam Algorithm is a basic multiplication principle applicable to all multiplication cases. It literally means 'crosswise and vertically' multiplication. It is based on a unique concept through which the partial products generation can be done with the simultaneous addition of these partial products.

The Pipelining in generation of partial products and their summation is obtained using Urdhava Triyakbhyam Algorithm. This algorithm can be generalized for N x N number of bits. Since the partial products and their sums are calculated in parallel, the multiplier is independent of the frequency of the clock used in processor. Thus the multiplier will require the same amount of calculation time for the product and hence it is independent of the clock frequency. The overall advantage is that it reduces the need of microprocessors to operate at higher clock frequencies. While a higher clock frequency results in increased processing power, its disadvantage is that it increases power dissipation which can cause higher device temperature of operations. By employing the pipelined multiplication, microprocessors designers can easily avoid these problems to avoid severe device failures.

The processing efficiency of multiplier can easily be increased by expanding the input and output data bus widths since it has a simple structure. Due to its simple structure, it can be easily laid out in a silicon chip. This Multiplier has the advantage that as the number of bits are increased, time delay and the area increases steadily as compared to other types of multipliers. Therefore it is time, area and power efficient. It can also be observed that this architecture is most efficient in terms of silicon area/speed.

#### III. IMPLEMENTATION OF 2x2 BIT MULTIPLIER

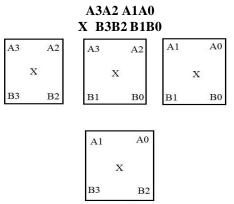

The method for two bit multiplication can be explained by, Considering two 4 bit numbers A and B where A = A1A0 and B = B1B0 as shown in Figure 1, Firstly, the lowest bits are multiplied which gives the Least Significant Bit (LSB) of the final product vertically. Then, the lowest bit of the multiplicand is multiplied with the next higher bit of the multiplier and added with, the product of LSB of multiplier and next higher bit of the multiplicand in crosswise manner. This sum gives second bit of the final product and the carry is added to the partial product obtained by multiplying the most significant bits to give the sum and carry. This sum is the third corresponding bit and carry becomes the fourth bit of the final product:

Figure 1: Block diagram of 2x2 bit Multiplier

The final result will be c2s2s1s0. This multiplication method is applicable for all the cases. The 2x2 bit multiplier module is implemented using four input AND gates & two half-adders as displayed in the block diagram in Fig 1

#### IV. IMPLEMENTATION OF 4X4 BIT MULTIPLIER

For higher number of bits in input, little modification is required. Divide the no. of bits in the inputs equally in two parts. In 4x4 bit multiplication, say multiplicand A=A3A2A1A0 and multiplier B= B3B2B1B0. Following is the output sequence for the multiplication result, \$7\$6\$5\$4\$3\$2\$1\$0.

Let's divide A and B into two parts, say — 'A3 A2' & 'A1 A0' for A and 'B3 B2' & 'B1B0' for B. Using the basics of Vertical and Crosswise Multiplication, and considering two bit at an instant and using two

| IJMER | ISSN: 2249–6645 |

numbers of two bit multiplier Section, we can obtain the following arrangement for 4x4 bit multiplication as shown in Figure 2.

Figure 2: 4 X 4 Multiplication

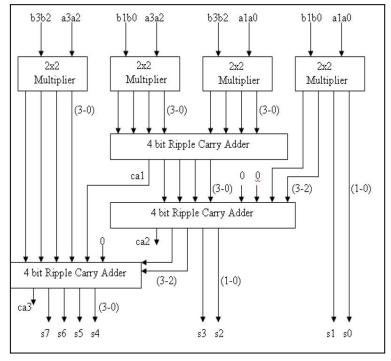

Each block as shown above is 2x2 bit multiplier. First 2x2 multiplier inputs are "A1 A0" and "B1 B0". The last block is 2x2 bit multiplier with inputs "A3 A2" and "B3 B2". The middle one shows two, 2x2 bit multiplier with inputs "A3A2" & "B1B0" and "A1A0" & "B3B2". So the final result" of multiplication, which is of 8 bit, "S7S6S5S4S3S2 S1S0".the block diagram of 4x4 bit Vedic Multiplier is shown in Figure 3. To get final product S7S6S5S4S3S2S1S0 four, 2-bit multipliers and three 4-bit Ripple Carry (RC) Adders are required. Here, the first 4-bit RC Adder is used to add two 4-bit operands obtained from cross multiplication of the two middle 2x2 bit multiplier modules. The second 4-bit RC Adder is used to add two 4-bit operands, i.e. concatenated 4-bit two grounded inputs & most significant two output bits at right hand most 2x2 multiplier block as shown in Figure 3 and one 4-bit operand we get as the output sum of first RC Adder. Its carry i.e. ca1 is forwarded to third RCA. Now the third 4-bit RCA is used to add two 4-bit operands, i.e. concatenated 4-bit (carry ca1, "0" & most significant two output sum bits of 2nd RC Adder and one 4-bit operand we get as the output sum of left hand most of 2x2 multiplier module. The arrangement of Ripple Carry Adder as shown in Figure 3 helps us to reduce delay

### V. IMPLEMENTATION OF 8x8 BIT MULTIPLIER

Algorithms for 8 X 8 Bit Multiplication Using Urdhva Triyakbhyam (Vertically and crosswise) for two Binary numbers:

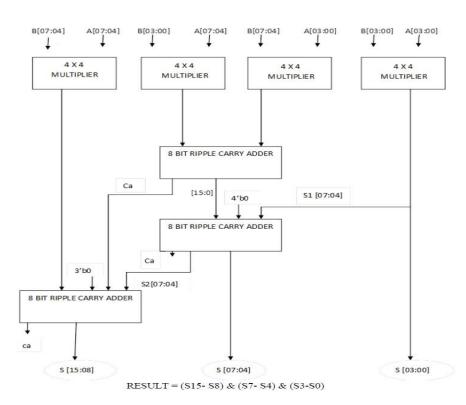

Figure 4: 8 X 8 Multiplication Block Diagram

The  $8x\ 8$  bit multiplier is structured using 4X4 bit blocks as shown in figure 4.7. In this figure the 8 bit multiplicand A can be decomposed into pair of 4 bits AH-AL. Similarly multiplicand B can be decomposed into BH-BL. The 16 bit product can be written as:

```

P = A \times B = (AH-AL) \times (BH-BL)

= AH \times BH+AH \times BL + AL \times BH+AL \times BL

```

The outputs of 4X4 bit multipliers are added accordingly to obtain the final product with the help of three ripple carry adders. Now the basic building block of 8x8 bits Vedic multiplier is 4x4 bits multiplier which implemented in its structural model. For bigger multiplier implementation like 8x8 bits multiplier the 4x4 bits multiplier units has been used as components which are implemented in DSCH3.5 and MICROWIND 3.1 and the structural modelling of above design shows fastest design

## VI. MGDI LOGIC DESIGN TECHNIQUE

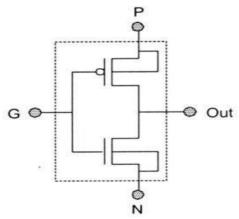

First the GDI basic cell was introduced by Arkadiy Morgenshtein in 2002 [5]. The basic GDI cell (figure 2) contains one nMOS and one pMOS transistors with four terminals: G, P, N and D. Input G is the common gate input of nMOS and pMOS transistors, input P is the outer diffusion node of pMOS transistor, input N is the outer diffusion node of MOS transistor, and output D is the common output diffusion node of both transistors. The GDI primitive cells are designed in twin-well CMOS or silicon on insulator (SOI) technologies.

Figure.5. Basic GDI cell

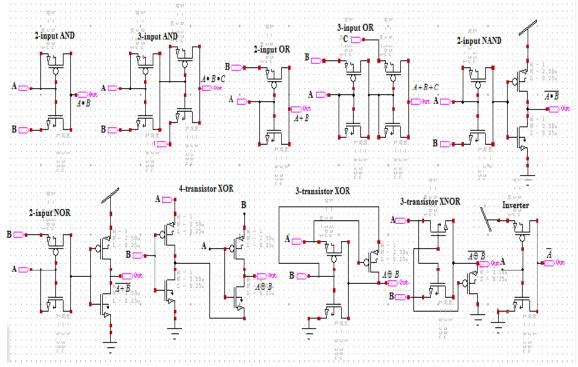

With few improvements in GDI technique, paper [8] presented MGDI cell for all basic gates with minimum power dissipation. Figure 3 shows the design of MGDI basic gates for inverter, 2 input AND, OR, NAND, NOR, and 3 transistor XOR gates. The operation of OR gate is described here. For OR gate, the source of pMOS is connected with input "B" and the source of nMOS is connected with input "A". The gate terminal G is connected with "A". When both the inputs are at low level then pMOS will operates in linear whereas nMOS is cut-off. When A is at high and B is at low level then pMOS is in linear region and nMOS is in linear region thereby producing the output as 1. Similarly for A at low level and B is at high level then pMOS is in linear and nMOS is also in linear region again producing the output as 1 Similarly when A and B both are at high level , then pMOS and nMOS are again in linear region thereby producing the output as 1.

Figure.6 Basic Digital Gates using MGDI technique

The comparative performance analysis [8] of MGDI, and CMOS logic is presented in Table 1. The comparative performance is done with respect to switching delay, transistor count and average power consumed by MGDI, and CMOS logic. The Comparative Table No.1 shows that the MGDI performance is better when compared to CMOS logic. CMOS technique uses double number of transistor compare to MGDI to realize any digital gates. The transistors used to design XOR and XNOR has only three transistors in MGDI whereas CMOS logic uses eight transistors.

## VII. Implementation Of Pipelined Multiplier Using MGDI Cell

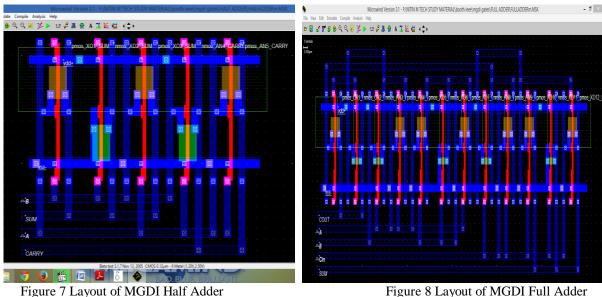

Binary Pipelined Multiplier for 2x2 bit 4x4 and 8x8 bit multiplication is designed using MGDI cell. First Basic gates, Half Adder, Full Adder and Ripple Carry Adder are designed using MGDI cell in MICROWIND & DSCH tools with 0.12µm technology with 1.2v supply voltage. The W/L ratio of both nMOS and pMOS transistors are taken as 1.0/0.12µm. To establish an unbiased testing environment, the simulation of multiplier designs have been carried out using comprehensive input bits, which covers every possible transition for multiplier and multiplicand bits. The cell delay are been measured from the instant inputs reach 50% of the voltage supply level to the instant the latest of the output signals reach the same voltage level. All the transitions from an input bit combination to another have been tested and the delay at each transition has been measured. The average has been considered as the cell delay. The power dissipation of multiplier is also measured for these input patterns and its average power has been reported.

Figure 7 Layout of MGDI Half Adder

Figure 9 Layout of MGDI 4 X 4 Multiplier

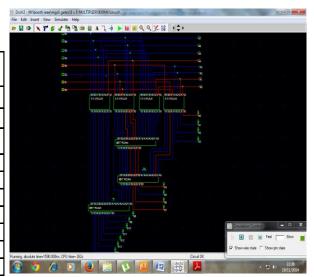

#### **VIII. Simulation Results**

Schematic of Multipliers are designed using DSCH 3.5 VLSI CAD tool and simulation is done while the Layout is generated using MICROWIND 3.1. For 8-bit multiplication, figure 9 shows simulation result for input multiplicand bit  $(19)_{10} = (00001011)_2$  and multiplier bit  $(11)_{10} = (00010011)_2$  and its output is  $(209)_{10} =$  $(000000011010001)_2$

#### Table 2 NALYSIS OF 4X 4MULTIPLIER

| S.No. | Primitive Cell    | Switching Delay (ns) |      | Power Dissipation |       | Area (µm) |       | Transistors Used |      |

|-------|-------------------|----------------------|------|-------------------|-------|-----------|-------|------------------|------|

|       |                   | CMOS                 | MGDI | CMOS              | MODI  | CMOS      | MCDI  | CMOS             | MGDI |

| 1     | 2-INPUT AND GATE  | 051                  | 0.2  | 0.528             | 0379  | 67.23     | 29.7  | 6                | 2    |

| 1     | 2-INPUT OR GATE   | 059                  | 0.23 | 0.977             | 0.098 | 97.7      | 29.8  | 6                | 2    |

| 3     | INVERTER          | 0.2                  | 0.2  | 0.867             | 0923  | 272       | 27.2  | 2                | 2    |

| 4     | 2-INPUT NAND GATE | 035                  | 0.41 | 1.615             | 0.779 | 107.7     | 63.03 | 4                | 4    |

| 5     | 2-INPUT NOR GATE  | 035                  | 0.42 | 0.887             | 0.608 | 583       | 63.02 | 4                | 4    |

| 6     | 2-INPUT XOR GATE  | 0.61                 | 0.27 | 0.0978            | 0.589 | 91        | 45.7  | 6                | 3    |

| 1     | 2-INPUTXNOR GATE  | 035                  | 0.25 | 0.833             | 0531  | 583       | 41    | 4                | 3    |

| 8     | 2:1MULTIPLEXER    | 034                  | 0.2  | 094               | 0517  | 97.7      | 32.4  | 6                | 2    |

| S.NO. | PARAMETERS                   | CMOS TECH.    | MGDITECH.   |  |

|-------|------------------------------|---------------|-------------|--|

| 1     | SWITCHING DELAY (Min., Max.) | 0.79,15.29 ns | 0.29,8.91ns |  |

| 2     | VERILOG FILE SIZE (Lines)    | 970           | 257         |  |

| 3     | NO. OF SYMBOLS USED          | 913           | 241         |  |

| 4     | COMPILED CELLS               | 429           | 216         |  |

| 5     | ROUTED WIRES                 | 88            | 109         |  |

| 6     | NO. OF NMOS TRANS, USED      | 399           | 92          |  |

| 7     | NO. OF PMOS TRANS. USED      | 399           | 124         |  |

| 8     | ELECTRICAL NODES COMPILED    | 542           | 130         |  |

| 9     | AREA (μ m²)                  | 20649.2       | 5770.1      |  |

| 10    | TRANSISTORS USED             | 798           | 218         |  |

## Table 3 ANALYSIS OF 8 X 8 MULTIPLIER

| S.NO. | PARAMETERS                   | CMOS TECH.   | MGDI TECH.  |  |

|-------|------------------------------|--------------|-------------|--|

| 1     | SWITCHING DELAY (Min., Max ) | 0.79,40.5 ns | 0.3,20.5 ns |  |

| 2     | VERILOG FILE SIZE (Lines)    | 3880         | 1261        |  |

| 3     | NO. OF SYMBOLS USED          | 3652         | 1193        |  |

| 4     | COMPILED CELLS               | 1716         | 1152        |  |

| 5     | ROUTED WIRES                 | 352          | 136         |  |

| 6     | NO. OF NMOS TRANS. USED      | 1596         | 488         |  |

| 7     | NO. OF PMOS TRANS. USED      | 1596         | 664         |  |

| 8     | ELECTRICAL NODES COMPILED    | 2168         | 714         |  |

| 9     | $AREA (\mu m^2)$             | 82596        | 31779.2     |  |

| 10    | TRANSISTORS USED             | 3192         | 1152        |  |

Figure 11 Simulation result (19)<sub>10</sub> x (11)<sub>10</sub>

## IX. CONCLUSION

This paper has presented the architecture design, logic design and circuit implementation of 8 Bit Pipelined Multiplier. The objective for Area, delay and power in Multipliers was carried out for bit multiplication using CMOS and MGDI techniques and Comparison with CMOS Technique are shown in Table 1, Table 2 and Table 3. The Pipelined Multiplier with MGDI technique gives less delay and less power dissipation with higher-speed of operation as compared to CMOS Technique.

## Acknowledgment

I would like to say thanks to my guide Associate Professor. Mr. M.Zahid Alam who gave their knowledge and time in order to complete this paper. This paper will never complete without the support faculty member of ECE department of L.N.C.T College, Bhopal.

#### REFERENCES

- [1] Massoud Pedram, "Design Technologies for Low Power VLSI", to spear in Encyclopedia of Computer Science and Technology, 1995.

- [2] Anantha P Chadrakasan and Robert W Brodersen, "Minimizing Power Consumption in CMOS Circuits", Proceedings of IEEE, Vol.83, No.4, April 1995.

- [3] Book by Dimitris Soudris, Christian Piguet and Costas Goutis, "Designing CMOS circuits for Low Power", May 2002

- [4] Pushpalata Verma (June 2012), "Design of 4x4 bit Vedic Multiplier using EDA Tool "International Journal of Computer Applications (0975 888) Volume 48– No.20, 32.

- [5] Arkadiy Morgenshtein, Alexander Fish, and Israel A. Wagner, "Gate Diffusion Input (GDI)-A Power-Efficient method for digital combinatorial circuits" IEEE Transactions on VLSI systems, vol.. 10,No. 5, October 2002

- [6] PhD Thesis by Gary W. Bewick, "Fast Multiplication: Algorithms and Implementation", Feb 1994

- [7] R.Uma and P. Dhavachelvan, "Modified Gate Diffusion Input Technique: A New Technique for Enhancing Performance in Full Adder Circuits", 2nd International

- [8] I.S. Abu I.S.Abu-Khater, A. Bellaouar, and M. I. Elmastry, "Circuit techniques for CMOS low-power high-performance multipliers," IEEE J. Solid-State Circuits, vol. 31, pp. 1535–1546, Oct. 1996.

- [9] Chidgupkar, P. D. and Karad, M.T., "The Implementation of Vedic Algorithms in Digital Signal Processing", Global Congress on Engineering Education, Vol. 8, No.2, 2004.

- [10] Himanshu Thapliyal and Vishal Verma, "High Speed Efficient Signed/Unsigned N X N Bit Multiplier Based On Ancient Indian Vedic Mathematics" proceedings of the 7th IEEE VLSI Design & Test Workshop, Bangalore, August 2003.