# Improving the Stability of Cascaded DC Power Supply System by Adaptive Active Capacitor Converter

B. Prudvi Kumar Reddy<sup>1</sup>, B. Amruth Kumar Reddy<sup>2</sup>

<sup>1</sup>M.Tech Student, Dr.K.V.S.R College of Technology, Kurnool, Andhra Pradesh <sup>2</sup> EEE Department, .K.V.S.R College of Technology, Kurnool,, Andhra Pradesh

Abstract: When all links are changes in the cascade is the corner of the shape in the dc division energy orbit (DEO). When resistances are intermission betwixt one by one stylish changes in that would possibly end up so the cascaded orbits are unsteady. They are antecedent we can place in a nearer to the useful in the cascaded orbit can be got in compelled to vary the supply they have load changes in the internal structure of the same regions in the electrical device they can be opposed in a quality of the characteristic of dc DEO. Throughout the Associate in nursing adaptation active device in the (AACC) we can know another determined in the cascaded orbit. Therefore the AACC was connected by side by side in the cascaded orbit's they can mediate in between the carries and completely a requirement of a notice then they carries the voltage with none modification in this subsystems. Then it will have a stylish to the customary have basic units to measuring in the dc DEO. When the AACC is additionally a similar bus device to cut back the output resistance of the supply device, therefore averting in a interiority have their load changes in the input resistance, of the cascaded orbit have their solutions then they becomes constant. We have important carrier device it will computing in the AACC adaptation in line with they have output energy to the cascaded orbit, they have energy vesting in the AACC that's way they will reduced and therefore they have a lot of energy in a reacting to the orbit so it is a best in the orbit of a submissive device. What\'s many, since no capacitance have a requirement among an AACC, when the cascaded orbits have their quantity of it slowly it will extend in time. They have activity fundamental truth to stop their magnificence thought in the AACC are mentioned throughout of this project, it can have four thousand eight hundred and zero watts cascaded orbit was contain a strive of process to move in a full-bridge changes they can be styli shed and evaluated. So when the simulation solutions have to clear the performance of the arrangement of AACC.

*Index Terms:* Active capacitor converter, adaptive control, cascaded System, modularization, stability.

# I. INTRODUCTION

The dc division energy orbit (DEO) has been used widely in such applications as space stations, aircraft, communication systems, industrial autonomous production lines and defense electronic power systems for the last 20 years [1]–[5], due to its flexile system configuration, high-efficiency energy conversion, and high-density power delivery capability .One of the dc DEO'S attractive characteristics is modularity design[6], in which each Subsystem is first designed individually as a module, and then all subsystems are integrated to form a dc DEO. The modularization characteristic of dc DEO cuts down the system's development cycles and costs effectively. In a dc DPS, there are various ways to connect the subsystems, among which, a typical connection style is cascaded Converters.

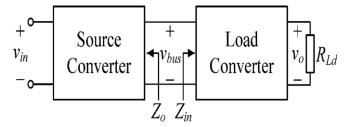

Fig. 1. Cascaded power supply system.

The cascaded system may have stability problem due to the interaction between the subsystems, even though each subsystem is individually well designed to be stable on its own [7]-[12]. This problem was first analyzed by idle brook [13]. It was shown that for the typical cascaded system shown in Fig. 1, the ratio of the source converter's output impedance Zo and the load converter's input impedance Zin, Zo /Zin, can be equivalently represented as the loop gain of the cascaded system. It was also pointed out that if both the ource converter and the load converter are stable individually, and Zo is less than Zin in the entire frequency ranges, the stability of the cascaded system will be guaranteed. This is the so-called Middle brook criterion. Subsequently, various impedance criteria aiming at a more accurate and practical prediction of the subsystem interaction had been developed in the last two decades [14]-[19]. Solutions for solving the instability problem have been proposed and can be broadly classified into two types: passive [20]-[22] and active [23]-[29] methods. Passive methods employ passive components, such as resistors, capacitors, and inductors, to improve system stability. A resistive load was added to modify load dynamic characteristics in [20], thereby improving system stability. Both RC and RL dampers were introduced to minimize the output impedance peak of the source converter in [21] and [22], thus ensuring Zo be less than Zin in the entire frequency ranges. The passive methods incur significant power dissipation. Active methods for stabilizing the system are based on modifying the control of the source converter [23]-[26]and/or load converter [27], or adding a power buffer between the source and load subsystems [28], [29]. The former approach, however, is usually complex in implementation and sometimes proposed conflicting with other control objectives. For the latter approach, the power buffer is connected in series in-between the subsystems, and would affect the impedance interaction during the transient that may not be acceptable in some applications. All the aforementioned solutions need to change the internal structure, including the main circuit and/or control circuit, of the dc DEO's subsystems, leading to redesign of the subsystems that have already been modularly designed. This contradicts with the objective of the modularity design of dc DPS and increases the system's development cycles. This paper introduces an adaptive active capacitor converter (AACC) connected in parallel with the remediate bus of the cascaded system. The AACC is equivalent to an adaptive bus capacitor varied with the cascaded system's output power; which reduces the output impedance of the source converter to avoid interacting with load converter's input impedance. As a result, the cascaded system becomes stable. The AACC only needs to detect the intermediate bus voltage without changing anything of the existing subsystems; hence, it serves as a standard stabilizer for dc DEO. Meanwhile, the equivalent capacitor of the AACC is adaptive, ensuring a minimal additional power loss and a better dynamic response of the system than that using a passive capacitor. Furthermore, as no electrolytic capacitor is required in the AACC, the lifetime of the cascaded system is prolonged. This paper first analyzes the impedance characteristics and instability problem of the cascaded system in Section II, and presents the concept, operating principle, ad control strategy of AACC in Section III. The design procedure and a design ample of AACC are given in Section IV. Section V shows he experimental results that verify the effectiveness of the proposed method. Finally, Section VI concludes this paper

# II. Impedance Characteristics And Instability Problem Of Cascaded System

# A. Review of Subsystem's Impedance Characteristics and Cause of Instability

For cascaded systems, the impedance characteristics of subsystems and the cause of instability have been studied extensively during the last two decades [30]–[35]. Some general conclusions are summarized as follows:

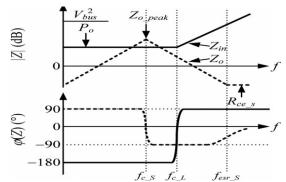

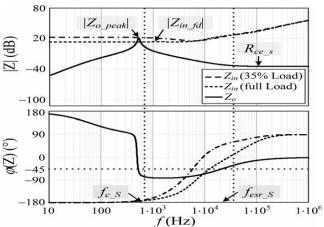

1) Impedance characteristic of Zo: Zo is the source converter's output impedance independent of its load resistor. As shown in the dotted line of Fig. 2, Zo is similar to the output impedance of an LC filter. If f < fc S, Zo presents

the characteristic of an inductor; and if f > fc S, Zo presents the characteristic of source converter's output filter capacitor. Here, fc S is the cutoff frequency of the source converter's voltage loop. Note that Zo 's peak value ,Zo peak, appears at fc S and is inversely proportional to source converter's output filter capacitor [30].

2) Impedance characteristic of Zin : In Fig. 2, the solid line

Represents Zin that is the input impedance of load converter

Operating in continuous current mode (CCM). If f < fc L, Zin behaves as a negative resistor, whose value equals to -V2

bus/Po [31], where Vbus is the intermediate bus voltage and Po is the load converter's output power

Fig. 2. Impedance interaction of the cascaded system.

| ~        |                  | $v_{bus}$          |                |                             |

|----------|------------------|--------------------|----------------|-----------------------------|

| $v_{in}$ | Source converter | C <sub>bus</sub> _ | Load converter | $\downarrow + v_o r R_{Ld}$ |

Fig. 3. Cascaded system with additional intermediate bus capacitor

Fig. 4. Equivalent model of Zo with additional intermediate bus capacitor

and if f > fc L, Zin behaves as an inductor. Here, fc L is the cutoff frequency of the load converter's voltage loop. Note that when f < fc L, the magnitude of Zin is inversely proportional to Po [32].

3) Cause of instability: In a cascaded system, as shown in

Figs. 1 and 2, if Zo is intersected with Zin and fc S is less than fc L, the cascaded system will be unstable [33]. In this case, the oscillation frequency is fc S that is unaffected by system's power [34].

The above analysis indicates that Zo is not affected by Po, and when f < fc L, the magnitude of Zin is inversely proportional to Po. Thus, the cascaded system is most likely to be unstable at full load because Zin is minimal and easily intersected with Zo at this condition. Note that the above conclusions are general and applicable to all dc–dc converters.

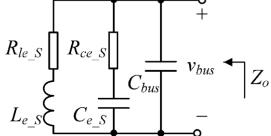

## B. Solving the Instability Problem by Adding Intermediate Bus Capacitor

There is nothing more desirable than a total separation between Zo and Zin to ensure that the cascaded system is stable. Since |Zo| peak| is inversely proportional to source converter's output filter capacitor [30], one intuitive way is to reduce the source converter' output impedance by adding an intermediate bus capacitor Cbus to the cascaded system, as shown in Fig. 3.Here, Cbus can be treated as an additional output filter capacitor of the source converter, and the equivalent LC output impedance model of source converter with Cbus is given in Fig. 4. In Fig. 4, Le S is the equivalent filter's inductor, Ce S is the equivalent filter's capacitor, Rle S is the parasitic resistor of

Fig. 5. Topology of the AACC introduced into cascaded system

*Le S*, and *Rce S* is the equivalent series resistor (ESR) of *Ce S* that can be measured from Fig. 2. Also, *Ce S*, *Le S*, and *Rle S* are expressed in (1)–(3), respectively  $Ce S = 1/2\pi Rce S fesr S \qquad (1)$  $Le S = 1/(2\pi fc S) 2 Ce S \qquad (2)$  $Rle S = Le S/Ce S \cdot /Zo \text{ peak/-} Rce S \qquad (3)$ where fesr S is the zero caused by the ESR of *Ce S*. According to (1)–(3), the peak value of *Zo* in Fig. 4 is derived as

/Zo peak/=Le S/(Ce S + Cbus) (Rle S + Rce S). (4)

Thus, in order to ensure that Zo < Zin in the entire frequency ranges, |Zo peak| must satisfy

$|Zo \text{ peak}| \leq V 2 \text{bus}/Po$

From (4) and (5), the required value of *C*bus can be obtained as

$$Cbus \ge Le \ SPo/V \ 2bus \ (Rle \ S + Rce \ S) - Ce \ S.$$

(6)

. (5)

. (7)

According to (6), the required *C*bus increases with the increase of *Po*, so, if a capacitor is employed, its value must be selected by (6) at full load. However, a larger *C*bus results in a smaller bandwidth of the source converter that is already modularly designed, leading to a poor dynamic performance [35]. Since the required *C*bus is relatively large, it inevitably adopts electrolytic capacitor, indicating a significant reduction of the lifetime [36].

In fact, the value of Cbus could be selected adaptively according to Po, as shown in (6), which keeps Cbus at its minimal required value for different loads. In this way, the cascaded system does not only ensure stable, but also achieves a better dynamic response.

## III. Topology And Control Of The Proposed AACC

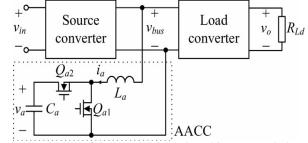

#### A. Topology of AACC

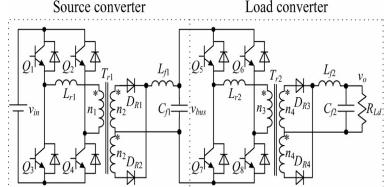

The adaptively varying Cbus mentioned in Section II can be

Emulated by a converter, as shown in the dashed block in Fig. 5. The converter is referred to as AACC. The AACC is composed of switches Qa1 and Qa2, inductor La, and capacitor Ca. It is connected to the intermediate bus of the cascaded system. By controlling La 's current appropriately, the terminal characteristic at the bus side of AACC will present an adaptively varying C bus that ensures the stability of the cascaded system and improves the dynamic response.

The AACC is also suitable for the cascaded system with multiple load converters. In this case, the AACC has the same operation principle with the system of Fig. 5, which just makes the source converter's output impedance lower than the total input impedance of the multiple load converters [17].

This paper analyzes the case shown in Fig. 5, but the conclusion applies to the system with multiple load converters.

## B. Control of AACC

Since the function of AACC is to emulate the adaptive Cbus, the current of La, ia, should be controlled as

$$ia(t) = Cbus(dvbus/dt)$$

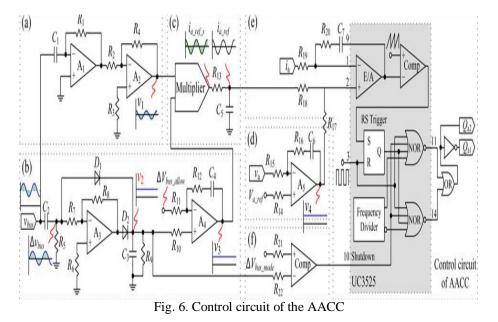

According to (6) and (7), it can be known that *ia* varies with *Po*. Considering *Po* can be reflected by the oscillation rippleof vbus,  $\Delta v$ bus [37], *ia* could be controlled by  $\Delta v$ bus, whose control cicuit is realized by a simple analog circuit, as shown inFig. 6. The control circuit for *ia* would only need to detect vbus without changing any part of the existing subsystems. Thus, the AACC can be designed as a standard module for dc DPS.As shown in Fig. 6, vbus first goes through a differential circuit (sub circuit A) to get the form of *ia* ref (*dv*bus/*dt*), defined as v1. Meanwhile,  $\Delta v$ bus is extracted from vbus by the filter comprising *C*2 and *R*5, and then it is sent to the rectifier circuit and a peak value detection circuit, producing  $\Delta v$ bus's magnitudev2. Then, v2 is compared with the preset allowable voltage ripple  $\Delta V$ bus allow, and the error is amplified by amplifier A4. The output of A4, v3, is the magnitude of *ia* ref. Therefore, *ia* refis adaptively varied by *Po*: a large *Po* brings a larger  $\Delta v$ bus, leading to a larger *ia* ref, which means a larger equivalent *C*bus of AACC; and on the contrary, a smaller *Po* gives a smaller equivalent *C*bus of AACC. Effectively, if *Po* is small enough,  $\Delta v$ bus will be less than  $\Delta V$ bus allow and *ia* ref will be zero, which means that *C*bus is no longer required at this time. Multiplying v1 with v3 by the multiplier, and the output,

*ia* ref *s*, is the required current, as seen in (7). In sub circuit C, *ia* ref *s* is filtered by R13 and C5 to produce *ia* ref, and only the Oscillation frequency component of *ia* ref *s* is retained. For proper operation of the AACC, *va* must be regulated at a value higher than *v*bus. A voltage closed loop must be included in the controller to enforce this (sub circuit D). Specifically, *va* is sensed and compared with the voltage reference *Va* ref, and the amplified error signal v4 is obtained. The sum of *ia* ref and *v*4with the weighted resistors R17 and R18, respectively, is used as the current reference of *ia*. The UC3525 controller is employed as the current regulator of *ia* and drive circuit of AACC. Also, *Qa*1 and *Qa2* are switched in a complementary manner. The shutdown signal of UC3525 is generated by sub circuit F that determines the working mode of AACC automatically. If the

Cascaded system is unstable, the magnitude of  $\Delta v$ bus,  $v^2$ , will be larger than the permitted value, denoted as  $\Delta V$ bus mode, and the shutdown signal of UC3525 will become low. In this case, the AACC works normally. Otherwise, the shutdowns signal will go high, shutting down the AACC. Here,  $\Delta V$ bus mode is set at a value below  $\Delta V$ bus allow to ensure that AACC works well.

## IV. Design Of AACC

#### A. Output Filter Capacitor Ca

With AACC, ignoring the switching harmonics of the cascaded system's intermediate bus voltage, vbus can be expressed as

vbus = Vbus + $\Delta V$ bus allow sin  $\omega t$ .

where V bus is the average value of v bus, and  $\omega$  is the angular frequency of the ripple in v bus, i.e.,  $\omega = 2\pi f c S$ .

The instantaneous input power of AACC can be obtained by

The instantaneous input power of AACC can be obtained by (7) = 1.00

(7) and (8), i.e., pa(t) = vbusia

$= (Vbus + \Delta Vbus allow \sin \omega t)Cbus\Delta Vbus allow \omega \cos \omega t.$  (9) Generally,  $\Delta V$ bus allow \_ Vbus; thus, (9) can be simplified

as

$$pa(t) = V bus C bus \Delta V bus allow \omega \cos \omega t.$$

(10)

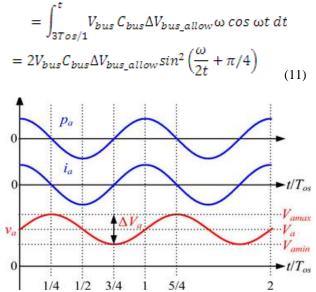

According to (7) and (10), the waveforms of the instantaneous input power Pa, inductor current ia, and output filter capacitor voltage va of AACC are depicted in Fig. 7. It can be seen that Ca is discharged from Tos /4 to 3Tos /4, and va decreases; and Ca is charged from 3Tos /4 to 5Tos /4, and va increases. Consequently, the maximum and minimum values of va occur, respectively, at Tos /4 and 3 Tos /4. The energy charging Ca from 3Tos /4 to 5Tos /4

$$\Delta E_a(t) = \int_{\frac{3Tos}{1}}^{t} P_a(t) dt$$

| IJMER | ISSN: 2249–6645 |

(8)

Fig. 7. Waveforms of instantaneous input power, inductor current, and output filter capacitor voltage of the AACC.

Here,  $\Delta Ea(t)$  can also be expressed as

$[\Delta Ea (t)=1/2CaV]_a^2(t) -1/2CaV]_(a \min)^2$ where Va min is the minimum voltage of the capacitor Ca. Putting (12) in (11) gives  $[1/2Ca [V]]_a^2(t) - V_(a \min)^2] = 2 \text{ VbusCbus } \Delta \text{Vbus}_allow \text{ Sin2} (\omega/2t + \pi/4)$

From (13), we have

(13)

$$V_{a}(t) = \sqrt{\frac{4VbusCbus\Delta VbusallowSin2\left(\frac{\omega}{2t} + \frac{\pi}{4}\right)}{Ca} + V_{a\ min}^{2}}$$

(14)

Substitution of t = 5Tos / 4 into (14), the maximum voltage of the capacitor *Ca* can be derived as

$$V_{a \max} = \sqrt{\frac{4V_{bus}C_{bus}\Delta V_{bus} \text{ allow}}{C_a} + V_{a \min}^2}$$

(15)

The average voltage of Ca can be approximated as

Vabc = (Va min + Va max)/2

$$= V_{a \min +} \frac{\sqrt{\frac{4 V_{bus} C_{bus} \Delta V_{bus} allow}{C_a} + V_{amin}^2}}{2}$$

(16)

$$\frac{4.0}{3.5}$$

$$3.0$$

$$V_a^* 2.5$$

$$2.0$$

$$V_a^* 2.5$$

$$2.0$$

$$V_{amin}^*$$

$$1.0$$

$$0.2$$

$$0.4$$

$$C_a^*$$

$$0.6$$

$$0.8$$

$$1$$

To ensure the proper operation of AACC, the instantaneous Voltage of *Ca* must always be higher than the input voltage of AACC, i.e.,  $va(t) \ge V$ bus. (17) We set *Va* min at *V*bus and  $\Delta v$ bus allow at 1% × *V*bus, and the Normalized *Va* max and *Va* dc with base of *V*bus are  $V_{amax}^*=V_{amax}/V_{bus}=\sqrt{(4\%/C_a^*)+1}$  (18)  $V_{abc}^*=V_{abc}/V_{bus}=1/2+\sqrt{(4\%/C_a^*)+1/4}$  (19)

Where C a is the normalized Ca with base of Cbus. According to (18) and (19), V \* a max and V \* adc as functions of C\*a are plotted in Fig. 8. Here, Va max increases as Ca reduces. In order to adopt film capacitors or ceramic capacitors instead of electrolytic capacitors, the value of Ca should be small enough However, this will result in high Va max. A high Va max induces high voltage stress on Qa1 and Qa2. Thus, Ca needs to be selected eclectically. Note that Ca must be selected at full load because it is the worst case for the cascaded system and the required Ca has the maximum value.

## B. Selection of Qa1 and Qa2

According to Fig. 5, the voltage stress of Qa1 and Qa2 is the Maximum voltage of va, i.e.,

$VQa \ 1 = VQa \ 2 = Va$ max.

(20)

The current stress of Qa1 and Qa2 is the maximum current of La, and can be derived from (7) and (8), i.e.,

$IQa \ 1 = IQa \ 2 = \omega C$ bus max $\Delta V$ bus allow (21)

Where C bus max is the required value of C bus at full load. The power devices for Qa1 and Qa2 could be chosen according to (20) and (21).

## C. Inductor of AACC

Two factors must be taken into consideration when choosing the value of La. One is to ensure that the inductor current is

Fig. 9. Cascaded system consisting of two phase-shifted full-bridge converters.

Capable of tracking the current reference and the other is that the inductor current ripple should be kept small.

Here, the AACC's inductor current, ia, needs to track the Oscillation ripple, whose oscillation frequency is the cutoff frequency of the source converter's voltage loop gain. Hence, the switching frequency of AACC, *fsa*, should be chosen much higher than the oscillation frequency *fc S*. In this case, the tracking speed of *ia* is ensured and it would be sufficient to choose the value of *La* with sole consideration given to the inductor current ripple.

As the two power switches of AACC operate in a complementary manner, the AACC is operating in continuous current conduction mode. Thus, the duty cycle of Qa1 is

$$dQa \ 1 \ (t) = 1 - V$$

bus  $va \ (t)$ .

When Qa1 is turned ON and Qa2 is turned OFF, the voltage across La is Vbus. This voltage causes *ia* to increase. The rippleof *ia* can be expressed as  $\Delta iLa = Vbus/La \cdot dQa \ 1 \ (t) \cdot 1/fsa$  (23)

$$La = (va(t) - Vbus) Vbus/va(t)\Delta iLa fsa$$

It can be seen from (24) that La varies with va (t) in a oscillation period.

(22)

. (24)

# D. Design Example

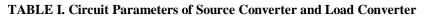

In this part, an AACC is designed for a cascaded system, as seen in Fig. 9, the system is composed by two phase-shifted full-bridge converters. Table I gives its parameters. In Fig. 9, both the source converter and load converter's voltage regulator are employing a PI controller. In this paper, fc Sand phase margin of source converter are set at 550 Hz and 45°, respectively, and fc L and phase margin of load converter are set at 5 kHz and 45°, respectively. According to the circuit and control parameters of the cascaded system, the Bode plots of the source converter's output impedance Zo and the load converter's input impedance Zin at different loads are plotted in Fig. 10. It can be seen that when the load is lower than 35% full load, Zo peak is less than Zin , and the cascaded system is stable. Otherwise, there is interaction between Zo and Zin, the system

| Source converter (360 V - 48 V 480 W 100 kHz) |                 |                 |                      |  |  |  |  |  |

|-----------------------------------------------|-----------------|-----------------|----------------------|--|--|--|--|--|

| Parameter                                     | value Parameter |                 | value                |  |  |  |  |  |

| $Q_1 \sim Q_4$                                | IRF840          | $L_{fl}$        | $150 \mu \mathrm{H}$ |  |  |  |  |  |

| $D_{R1} \sim D_{R2}$                          | DSEP15-06       | $C_{f1}$        | 680 µF               |  |  |  |  |  |

| Winding Turns<br>Ratio of $T_{r1}$            | 5:1             | $L_{r1}$        | 2 <i>µ</i> H         |  |  |  |  |  |

| $K_p$                                         | 3               | $K_i$           | 1000                 |  |  |  |  |  |

| Load converter (48 V – 12 V 480W 100 kHz)     |                 |                 |                      |  |  |  |  |  |

| Parameter                                     | value           | Parameter       | value                |  |  |  |  |  |

| $Q_5 \sim Q_8$                                | IXTP44N10T      | $L_{f2}$        | 2.2 μH               |  |  |  |  |  |

| $D_{R3} \sim D_{R4}$                          | DSA60C100PB     | C <sub>f2</sub> | 4700 μF              |  |  |  |  |  |

| Winding Turns<br>Ratio of $T_{r2}$            | 3:1             | $L_{r2}$        | 1 <i>µ</i> H         |  |  |  |  |  |

| $K_p$                                         | 8               | $K_i$           | 1500                 |  |  |  |  |  |

Fig. 10. Impedances of the source and load converters at different loads

Will become unstable, and the AACC is needed. In practice, the impedance characteristics of Zo and Zin can be measured by a network analyzer without knowing the intrinsic parameters of the subsystems. From Fig. 10, it can be seen that, Zo peak = 13.5  $\Omega$ , the input impedance of load converter at full load Zin f d is equal to 4.8  $\Omega$ , Rce S = 0.017  $\Omega$ , fc S = 550 Hz, and fesr S = 22.5 kHz. Using (1)–(3) and (7), we can calculate the oscillation angular frequency and Cbus max, i.e.,  $\omega = 2\pi fc S = 3455$  rad/s and Cbus max = 1950  $\mu$ F.

Setting  $\Delta v$  bus allow at 1% V bus, the main circuit parameters of AACC can be designed as follows:

- 1) We choose  $Ca = 20 \ \mu\text{F}$  (film capacitors, EACO-STH

- 200 V/20  $\mu$ F), then  $C * a = 20 \mu$ F/1950  $\mu$ F = 0.01.

2) Considering Vbus = 48 V and (18),  $VQa1 = VQa2 = Va \max 110$  V. By (21), IQa1 = IQa2 = 3 A. Here, FDMS2572 (4.5 A/150 V) with Rds(ON) of 0.09  $\Omega$  isodopted.

- 3) Considering fc S = 550 Hz, fsa is chosen as 100 kHz that is much higher than 550 Hz.

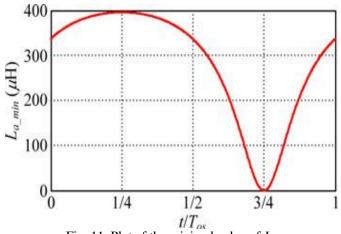

- 4) Setting  $\Delta iL$  max = 20% IQa1 = 0.6 A and from (14) and (24), the curve of minimum value of La, La min, in an oscillation period can be plotted in Fig. 11, where the

Fig. 11. Plot of the minimal value of La

| TABLE II. Components of Aacc, Passive C | apacitor Solution, and The Original cascaded System |

|-----------------------------------------|-----------------------------------------------------|

|-----------------------------------------|-----------------------------------------------------|

| Components of AACC                     |                                              |                                       |                 |    |          |  |  |

|----------------------------------------|----------------------------------------------|---------------------------------------|-----------------|----|----------|--|--|

| Main circuit                           |                                              |                                       | Control circuit |    | circuit  |  |  |

| Component                              |                                              | Part number                           | IC              |    | Quantity |  |  |

| $Q_{a1}$                               |                                              | FDMS2572 (4.5A/150V)                  | TL074           |    | 2        |  |  |

| $Q_{a2}$                               |                                              | FDMS2572 (4.5A/150V)                  | TL072           |    | 1        |  |  |

| $L_a$                                  | NCD EE33/14/13                               |                                       | LM393           |    | 1        |  |  |

| $C_a$                                  |                                              | EACO-STH 200 V/20 $\mu$ F             | SG3525          |    | 1        |  |  |

|                                        | С                                            | omponents of passive capacito         | r solution      |    |          |  |  |

| Componen                               | t                                            | Part number                           |                 |    | Quantity |  |  |

| $C_{bus}$ (1950 $\mu$                  | $C_{bus}$ (1950 $\mu$ F) Jianghai CD29S PJ 1 |                                       | /390 µF         |    | 5        |  |  |

| Components of original cascaded system |                                              |                                       |                 |    |          |  |  |

| Source converter                       |                                              |                                       |                 |    |          |  |  |

| Main circuit                           |                                              |                                       | Control circuit |    | circuit  |  |  |

| Component                              |                                              | Part number                           | IC              |    | Quantity |  |  |

| $Q_1 \sim Q_4$                         |                                              | IRF840 (8A/500V)                      | TL074           |    | 1        |  |  |

| $D_{R1} \sim D_{R2}$                   |                                              | DSEP15-06A (15A/600V)                 |                 |    | 1        |  |  |

| $T_{r1}$                               |                                              | NCD EE42/21/20                        | LM393           |    | 3        |  |  |

| $L_{r1}$                               |                                              | NCD EE25/10/7                         | TLP521-1        |    | 1        |  |  |

| $L_{f1}$                               |                                              | NCD EE55/28/25                        | HCPL3120        |    | 4        |  |  |

| $C_{f1}$                               | Jic                                          | anghai CD294 100 V/680 $\mu$ F        | UCC3895         |    | 1        |  |  |

| Load converter                         |                                              |                                       |                 |    |          |  |  |

| Main circuit                           |                                              | Control circuit                       |                 |    |          |  |  |

| Component                              |                                              | Part number                           | IC              |    | Quantity |  |  |

| $Q_5 \sim Q_8$                         |                                              | XTP44N10T (44A/100V) TL074            |                 |    | 1        |  |  |

| $D_{R3} \sim D_{R4}$                   | DSA60C100PB (60A/100V)                       |                                       | TL072           |    | 1        |  |  |

| $T_{r2}$                               |                                              | NCD EE42/21/20                        | LM393           |    | 3        |  |  |

| $L_{r2}$                               |                                              | NCD EE25/10/7                         | TLP521-1        |    | 1        |  |  |

| $L_{f^2}$                              |                                              | NCD EE42/21/20                        | HCPL3120        |    | 4        |  |  |

| $C_{f^2}$                              | Jic                                          | <i>Jianghai</i> CD294 50 V/4700 μF UC |                 | 95 | 1        |  |  |

Maximum value of *La* min is 395  $\mu$ H. Here, we choose *La* = 395  $\mu$ H.

Considering the cost is a matter of concern in practical, Table II lists the selected components of AACC, passive capacitor solution, and the original cascaded system. Currently, the cost of AACC is slight higher than the passive capacitor solution, and accounts for about 9% of the original cascaded system.

# V. Experimental Verification

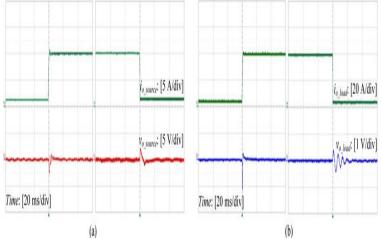

In order to verify the validity of the proposed AACC, a prototype has been built and tested. The parameters of the prototype have been given in Section IV-D. Fig. 12 shows the steady-state experimental waveforms of the source converter and load converter operating individually. Fig. 13(a) and (b) shows the individual dynamic waveforms of the source and load converters when their load steps between full load and 10% full load, respectively. As seen from the figures, both source and load converters are stable and working well.

Fig. 13. Individual dynamic waveforms of the source and load converters when their load steps between full load and 10% full load: (a) source converter and (b) load converter

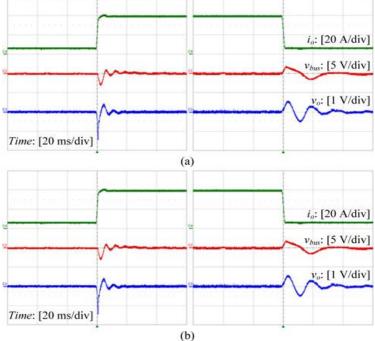

Considering that the cascaded system can be stable with a 1950  $\mu$ F passive capacitor (*C*bus max) or AACC in the full load range. Fig. 18 compares their dynamic performance when the load steps between full load and 10% full load. It shows that the system with AACC has a faster dynamic response than that of the system using the passive capacitor solution. According to the reason can be explained as follows. The equivalent capacitor of AACC is adaptively varied by the load. Its value is always smaller than 1950  $\mu$ F and approaches zero when the system is stable. And a smaller *C*bus, of course, means a faster dynamic performance for the cascaded system. In addition, compared with Figs. 13 and 18(b), it seems that the cascaded system with AACC has a similar dynamic performance with its individual subsystems.

Fig. 14. Waveforms of cascaded system when the load steps between full load and 10% full load: (a) with the AACC (b) without the AACC

# VI. Conclusion

When the AACC is a good suggests that to resolve the instability downside of the dc distributed power supply. In the presents days they will offers the AACC as identical adjective bus capacitance will be changeable per then the cascaded system have their output power, so we can avert the electrical resistance can communicate to the cascaded system with the quantity of the output electrical resistance in the supply convertor. Betting in the edge of the undisturbed conditions in the cascaded system, therefore the AACC is adjectively functionaries. Once the move in the cascaded system was broad in the AACC supply to the additional power of the produce to

the bigger importance capacitance. Once they can moves in the cascaded system have a very small value, when the AACC can supply less power in the produce have smaller importance capacitance. Once there is no moves in a cascaded system they have a periodic voltage among in a permutable to the opportunity, of the AACC are going to be stop working. They can have employment in the AACC doesn't solely make sure the undisturbed conditions in a cascaded system, however additionally unpleasant situation in the important loss. When the energy has a lot of reactions in the cascaded system have additionally then see a better change in the employment of a yielding capacitance. Moreover, there is an electrolytic employed during AACC of the incorporates a hopeful effect in a organized period.

They will tally in the present technique, the projected convertor solely has they discover the cascaded system to the bus voltage while not dynamic something in the present subsystems, thus they will be a stylish to the customary can be measuring in the dc DPS. Then AACC will been ascertain carefully see the power values that is four thousand eight hundred zero watts and we can see different voltage ratings in the cascaded system. After we can see the exact output results of the experimental in the validity of the analysis.

#### REFERENCES

- [1] F. Blaabjerg, A. Consoli, J. A. Ferreira, and J. D. van Wyk, "The future of electronic power processing and conversion," IEEE Trans. Power Electron., vol. 20, no. 3, pp. 715-720, May 2005.

- J. D. van Wyk and F. C. Lee, "Power electronics technology-Status and future," in Proc. CPES, 1999, pp. 61-70. [2]

- K. T. Kornegay, "Design issues in power electronic building block (PEBB) system integration," in Proc. IEEE VLSI, [3] Apr. 1998, pp. 48-52.

- [4] T. Ericsen, "Power electronic building blocks—A systematic approach to power electronics," in Proc. IEEE Power Eng. Soc. Summer Meeting, 2000, pp. 1216–1218.

- [5] D. Boroyevich, I. Cvetkovi c, D. Dong, R. Burgos, F. Wang, and F. C. Lee, "Future electronic power distribution systems—A contemplative view," in Proc. IEEE OPTIM, May 2010, pp. 1369–1380.

- S. Luo, "A review of distributed power systems part I: DC distributed power system," IEEE Aerosp. Electron. Syst. [6] Mag., vol. 20, no. 8, pp. 5-16, Aug. 2005.

- L. R. Lewis, B. H. Cho, F. C. Lee, and B. A. Carpenter, "Modeling, Analysis and design of distributed power [7] systems," in Proc. IEEE PESC, Jun. 1989, pp. 152-159.

- [8] G. A. Franz, G. W. Ludwig, and R. L. Steigerwald, "Modeling and simulation of distributed power systems," in Proc. IEEE PESC, 1990, pp. 606-610.

- S. Schulz, B. H. Cho, and F. C. Lee, "Design considerations for a distributed power system," in Proc. IEEE PESC, [9] 1990, pp. 611-617.

- [10] B. H. Cho and B. Choi, "Analysis and design of multi-stage distributed power systems," in Proc. Int. Telecomm. Energy Conf., Kyoto, Japan, Nov. 1991, pp. 220-226.

- A. Emadi, "Modeling of power electronic loads in ac distribution systems using the generalized state-space averaging [11] method," IEEE Trans. Ind. Electron., vol. 51, no. 5, pp. 995-1000, Oct. 2004.

- [12] A. Khaligh, "Realization of parasitics in stability of dc-dc converters loaded by constant power loads in advanced multiconverter automotive systems," IEEE Trans. Ind. Electron., vol. 55, no. 6, pp. 2295-2305, Jun. 2008.

- R. D. Middlebrook, "Input filter considerations in design and application of switching regulators," in Proc. IEEE IAS, [13] 1979, pp. 366-382.

- C. M. Wildrick, F. C. Lee, B. H. Cho, and B. Choi, "A method of defining the load impedance specification for a [14] stable distributed power system," IEEE Trans. Power Electron., vol. 10, no. 3, pp. 280-285, May 1995.

- P. Huynh and B. H. Cho, "A new methodology for the stability analysis of large-scale power electronics systems," [15] IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 45, no. 4, pp. 377-385, Apr. 1998.

- S. D. Sudhoff, S. F. Glover, P. T. Lamm, D. H. Schmucker, and D. E. Delisle, "Admittance space stability analysis of [16] power electronic systems," IEEE Trans. Aerosp. Electron. Syst., vol. 36, no. 3, pp. 965-973, Jul. 2000.

- X. Feng, J. Liu, and F. C. Lee, "Impedance specifications for stable DC distributed power systems," IEEE Trans. [17]

- *Power Electron.*, vol. 17, no. 2, pp. 157–162, Mar. 2002. X. Wang, R. Yao, and F. Rao, "Three-step impedance criterion for small signal stability in two-stage dc distributed [18] power systems," IEEE Trans. Power Electron. Lett., vol. 1, no. 3, pp. 83-87, Sep. 2003.

- T. Suntio, I. Gadoura, and K. Zenger, "Input filter interactions in peakcurrent-mode-controlled buck converter [19] operating in CICM," IEEE Trans. Ind. Electron., vol. 49, no. 1, pp. 76-86, Feb. 2002.

- X. Wang, D. Vilathgamuwa, and S. Choi, "Decoupling load and power system dynamics to improve system [20] stability," in Proc. IEEE PEDS, 2005, pp. 268-273.

## BIOGRAPHIES

**B. Prudvikumarreddy** is born in 1990 in India. He is graduated from JNTUA University in 2012. Presently he is doing Post graduation in Power Electronics and Electrical Drives Specialization at J.N.T.U.A, Anantapur His main areas of interest include Induction motor drives, Electrical machines, Power Electronics, & power systems.

**B. AmruthKumarreddy is** born in 1987 in India. He is graduated from JNTUH University in 2008 and pursued Post graduation from the JNTUA University. He is currently working as a Assistant professor in the department of electrical and electronics engineering Dr. K.V.S.R institute of technology, kurnool, Andhra Pradesh, India. He has 5 years of teaching experience. He has attended several National workshops. His main areas of research include Induction motor drives, Electrical machines, FACTS and power convertors.