# New Topology for Transformer less Single Stage -Single Switch AC/DC Converter

Nirma Peter<sup>1</sup>, Surya Natrajan<sup>2</sup>

<sup>1</sup>(Student, Department of Electrical and Electronics, FISAT, MG University, Kerala, India) <sup>2</sup>(Assistant Professor, Department of Electrical and Electronics, FISAT, MG University, Kerala, India)

**ABSTRACT :** This paper presents a transformer less single-stage single-switch ac/dc converter suitable for universal line applications (90–270 Vrms). The topology consists of a buck-type power-factor correction (PFC) cell with a buck-boost dc/dc cell and part of the input power is directly coupled to the output after the first power processing. With this direct power transfer and sharing capacitor voltages, the converter is able to achieve efficient power conversion, high power factor, low voltage stress on intermediate bus (less than 120 V) and low output voltage without a high step-down transformer. The absence of transformer reduces the size of the circuit, component counts and cost of the converter. Unlike most of the boost-type PFC cell, the main switch of the proposed converter only handles the peak inductor current of dc/dc cell rather than the superposition of both inductor currents. Tight voltage regulation is provided by using PID controller. Detailed analysis and design procedures and simulation of the proposed circuit are given.

**Keywords:** Direct power transfer (DPT), integrated buck–buck–boost converter (IBuBuBo), powerfactor correction (PFC), single-stage (SS), transformer less.

### I. Introduction

The use of rectifiers in industrial applications started at the era of mercury converters with the electromechanical contact converter. DC machines are common in day to day use. But the supply that we get from power companies is AC. To use those machines AC supply has to be turned into DC supply by the use of a rectifier. The basic block diagram of AC/DC converter is shown in Figure 1.1. A rectifier is an electrical device that converts the incoming AC (alternating current) from a transformer or any other ac power source to pulsating DC (direct current). Rectifier may be made of diodes, solid states, vacuum tube, mercury arc valves and other components. Rectifiers are widely used in non linear loads which are connected with distribution systems which plays an important role in power system network (ex: UPS, discharge lamp, television, computer, fax machines, ferromagnetic devices, arc furnaces, energy savers etc).

The research on single-stage PFC ac/dc converters can be traced back to the early 1990s .Single-stage (ss) ac/dc converters have lot of applications because of its cost effectiveness, compact size, and simple control mechanism. Among existing SS converters, most of them are comprised of a boost power-factor correction (PFC) cell followed by a dc/dc cell. Dc/dc cell is used for output voltage regulation . Several such methods are shown in references [1]–[7] .But their intermediate bus voltage is usually greater than the line input voltage and goes beyond 450 V at high-line application. Also there are a lot of efforts to limit this bus voltage, it is still near or above the peak of the line voltage due to the nature of boost-type PFC cell. In addition, the other drawbacks of the boost-type PFC cell are that it cannot limit the input inrush current and provide output short-circuit protection[14].

Figure 1.1: Block Diagram Of AC/DC Converter

Some multistage power electronics system (e.g., in data center, electrochemical and petrochemical industries), the isolation has been done in the PFC stage, the second transformer in the dc/dc cell for the sake of isolation is considered as redundant. Hence, nonisolated ac/dc converter can be employed to reduce unnecessary or redundant isolation and enhance efficiency of the overall system. Besides, leakage inductance of the transformer causes high spike on the active switch and lower conversion efficiency. To protect the switch, snubber circuit is usually added resulting in more component counts[13]. For low voltage application (e.g., $\leq$ 48V), this high intermediate bus voltage increases components stresses on the dc/dc cell. This problem can be overcome by using a simple step-down dc/dc cell (i.e. buck or buck–boost converter).Extremely narrow duty cycle is needed for the conversion.This leads to poor circuit efficiency and limits the input voltage range for getting better performance.

Several methods were introduced to reduce the bus voltage much below the line input voltage during the years 2007-2011. Several such topologies have been reported in the references [9], [10], [13], [15]–[18]. Although the recently reported IBoBuBo converter in [13] is able to limit the bus voltage under 400 V, it cannot be applied to the low-voltage application directly due to the boost PFC cell. On the other hand, the converters in [9], [10], [15]–[18] employ different PFC cells to reduce the intermediate bus voltage. Among those converters in [9] and [15] use a transformer to achieve low output voltage either in PFC cell or dc/dc cell. Therefore, the leakage inductance is unavoidable. Converters in [10], [17], and [18], employ a buck-boost PFC cell resulting in negative polarity at the output terminal. In addition, the topologies in references [18] and [10] process power at least twice resulting in low power efficiency. Moreover, the reported converters, in [16], and [17], consist of two active switches leading to more complicated gate control. Apart from reducing the intermediate bus voltage, the converter in [19] employs resonant technique to further increase the step-down ratio based on a buck converter to eliminate the use of intermediate storage capacitor. The converter features with zero-current switching to reduce the switching loss. However, without the intermediate storage, the converter cannot provide hold-up time and presents substantial low-frequency ripples on its output voltage. Besides, the duty cycle of the converter for high-line input application is very narrow, i.e., < 10%. This greatly increases the difficulty in its implementation due to the minimum on-time of pulse-width-modulation (PWM) IC and rise/fall time of MOSFET.

To tackle the aforementioned problems, an intergrated buck-buck-boost (IBuBuBo) converter with low output voltage is proposed. This proposed circuit consists of a buck converter, used as PFC cell and a buck-boost converter as a dc/dc converter. This circuit is able to limit the bus voltage below the input voltage effectively. In addition, by In addition, by sharing voltages between the intermediate bus and output capacitors, further reduction of the bus voltage can be achieved. Therefore, a transformer is not needed to obtain the low output voltage. The converter is able to achieve:

1) low voltage stress on intermediate bus (less than 120 V);

2) high PF, compact size, Less cost;

3) low intermediate bus and output voltages in the absence of transformer;

4) simple control structure with a single-switch;

5) positive output voltage;

6) high conversion efficiency due to part of input power is processed once and

7) input surge current protection because of series connection of input source and switch.

### **II. Direct Power Transfer**

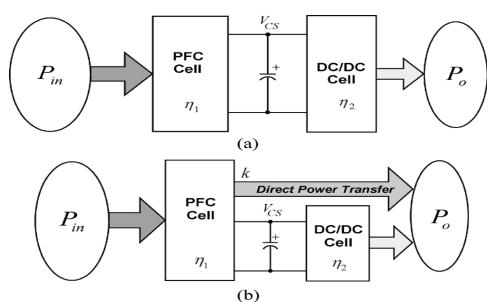

In a conventional two-stage or S PFC ac/dc converter, there are two functional cells, i.e., PFC cell and dc/dc cell. AC input power is first transferred into somewhat pulsating dc power stored on intermediate bulk capacitors by the PFC cell. The stored dc power on the bulk capacitors is processed again by the dc/dc cell to the desired dc output power. So the input power is processed twice to reach the output, as shown in Fig. 2.1(a). Assuming the PFC cell has unity input power factor, and the efficiency of the PFC cell and pc/dc celh<sub>2</sub> are and, respectively, we have output power

$$P_0 = P_{in} \eta_1 \eta_2 \tag{1}$$

and the resultant efficiency of SS PFC ac/dc converter is

$$\eta = \eta_1 \eta_2 \tag{2}$$

From the above equations, we can see that the dual power processing approach means lower conversion efficiency since it is the product of the efficiency of each power conversion

Figure. 2.1. Power transfer block diagrams of PFC ac/dc converters: (a) conventional power transfer and (b) proposed power transfer with DPT concept.

Direct power transfer approaches will allow a part of the input power to be processed only once and let the remaining input power to be processed twice while still achieving both high power factor and tight output

$$P_0 = P_{in}\eta_1 k + P_{in}\eta_1\eta_2(1-k)$$

<sup>(3)</sup>

regulation. Those power transfer approaches provide a new way to achieve more efficient and higher power rating PFC converters than the conventional double power processing approach. A block diagram of the proposed power transfer approach with the DPT concept is expressed in Fig. 2 .1(b). In Fig. 2.1(b), (1-k) portion of the power from the PFC cell is directly transferred to the output, and the remaining power from PFC cell is stored in the intermediate bus capacitor and then processed by the dc/dc cell. Based on this concept, we have so the efficiency of this S PFC ac/dc converter is

$$\eta = \eta_1 \eta_2 + k \eta_1 (1 - \eta_2) \tag{4}$$

Comparing (2) with (4), it is clear that the converter with the DPT generally has higher efficiency than its counterpart without the DPT approach, simply because the converter with the DPT concept follows an inequality

$$\eta_{1}\eta_{2} + k\eta_{1}(1-\eta_{2}) > \eta_{1}\eta_{2}$$

where  $_{k} < 1.\eta_{1} < 1.and\eta_{2}1.$

(5)

The above efficiency comparison enhances our understanding why the DPT concept will help build an inherently more efficient PFC converter

### III. Single-Stage PFC Converter

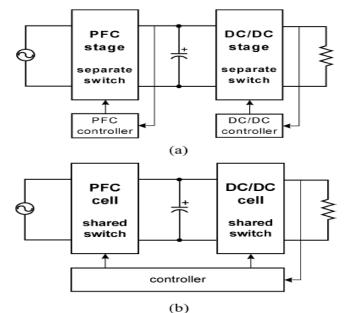

Power factor correction (PFC) techniques have become increasingly important since several regulations that are used to limit harmonic injection to the power utilities have been enacted recently. There are two basic PFC approaches, namely, active PFC and passive PFC. Active PFC, classified by the system configurations, can be categorized into two-stage and single-stage SS schemes. A two-stage scheme results in high power factor and fast response output voltage regulation by using two independent controllers and optimized power stages, as shown in Fig. 3.1(a). The main drawbacks of this scheme are its relatively higher cost and larger size resulted from its complicated power stage topology and control circuits, particularly in low power applications.

An SS scheme combines the PFC cell and dc/dc power conversion cell into one stage, and typically uses only one controller and shares power switches, as shown in Fig. 3.1(b). It should be pointed out that from the viewpoint of functionality, in order to get high power factor and regulated output, an SS converter actually still needs to complete PFC and dc/dc regulating tasks as a two-stage converter. Usually, the high power factor of an SS PFC converter is guaranteed by operating the PFC cell in discontinuous current mode (DCM), while the fast response output regulation is achieved by the dc/dc cell. Although the single-stage scheme is especially

attractive in low cost and low power applications due to its simplified power stage and control circuit, major issues still exist, such as low efficiency and difficulty being moved to higher power level, and high as well as wide-range intermediate dc bus voltage stress.

Figure. 3.1. Functional block diagram of PFC converters: (a) two-stage PFC converter and (b) typical singlestage PFC converter.

### **IV.** Proposed Circuit and Its Operating Principle

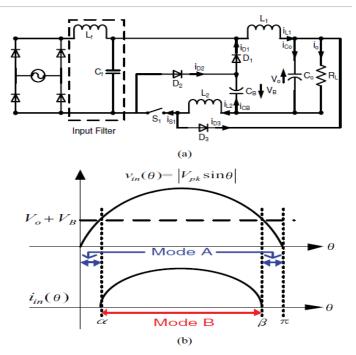

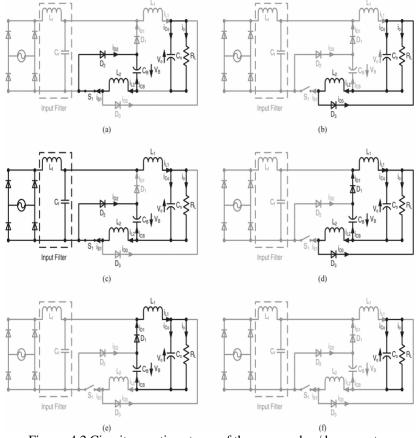

The proposed I Bu Bu Bo converter, which consists of the merging of a buck PFC cell  $(L_1, S_1, D_1, C_o, C_B)$ and a buck-boost dc/dc cell  $(L_2, S_2, D_2, D_3, C_o, C_B)$  is illustrated in Fig. 4.1(a). Although L2 is on the return path of the buck PFC cell, does not contribute to the cell electrically. Thus, L2 is not considered as in the PFC cell. Moreover, both cells are operated in discontinuous conduction mode (DCM) so there are no currents in both inductors L1 and L2 at the beginning of each switching cycle t0. Due to the characteristic of buck PFC cell, there are two operating modes in the circuit.

Figure 4.1: (a) Proposed IBuBuBo SS ac/dc converter. (b) Input voltage and current waveforms

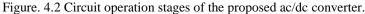

ModeA(vin  $(\theta) \le VB + Vo$ ): When the input voltage vin  $(\theta)$  is smaller than the sum of intermediate bus voltage VB, and output voltage Vo, the buck PFC cell becomes inactive and does not shape the line current around zero-crossing line voltage, owing to the reverse biased of the bridge rectifier. Only the buck–boost dc/dc cell sustains all the output power to the load. Therefore, two dead-angle zones are present in a half-line period and no input current is drawn as shown in Fig. 4.1(b). The circuit operation within a switching period can be divided into three stages and the corresponding sequence is Fig. 4.2(a),(b), and (f). Fig. 4.3(a) shows its key current waveforms.

- 1) Stage 1 (period d1Ts in Fig. 4.3) [see Fig. 4.2(a)]: When switch S1 is turned ON, inductor L2 is charged linearly by the bus voltage VB while diode D2 is conducting. Output capacitor Co delivers power to the load.

- 2) Stage 2 (period d2Ts in Fig. 4.3) [see Fig. 4.2(b)]: When switch S1 is switched OFF, diode D3 becomes forward biased and energy stored in L2 is released to Co and the load.

- 3) Stage 3 (period d3Ts d4Ts in Fig. 4.3) [see Fig. 4.2(f)]: The inductor current iL2 is totally discharged and only Co sustains the load current.

Mode B (vin ( $\theta$ ) > VB + Vo ): This mode occurs when the input voltage is greater than the sum of the bus voltage and output voltage. The circuit operation over a switching period can be divided into four stages and the corresponding sequence is Fig. 4.2(c), (d), (e), and (f). The key waveforms are shown in Fig. 4.3(b).

- 1) Stage 1 (period d1Ts in Fig. 4.3) [see Fig. 4.2(c)]: When switch S1 is turned ON, both inductors L1 and L2 are charged linearly by the input voltage minus the sum of the bus voltage and output voltage (vin  $(\theta) VB Vo$ ), while diode D2 is conducting.

- 2) Stage 2 (period d2Ts in Fig. 4.3) [see Fig. 4.2(d)]: When switch S1 is switched OFF, inductor current iL1 decreases linearly to charge CB and Co through diode D1 as well as transferring part of the input power to the load directly. Meanwhile, the energy stored in L2 is released to Co and the current is supplied to the load through diode D3. This stage ends once inductor L2 is fully discharged.

- 3) Stage 3 (period d3Ts in Fig. 4.3) [see Fig. 4.2(e)]: Inductor L1 continues to deliver current to Co and the load until its current reaches zero.

- 4) Stage 4 (period d4Ts in Fig.4.3) [see Fig. 4.2(f)]: Only Co delivers all the output power.

Figure. 4.3. Key waveforms of the proposed circuit

# V. Design Consideration

To simplify the circuit analysis, some assumptions are made as follows:

1) all components are ideal;

2) line input source is pure sinusoidal, i.e.  $vin(\theta) = Vpksin(\theta)$  where Vpk and  $\theta$  are denoted as its peak voltage and phase angle, respectively;

3) both capacitors CB and Co are sufficiently large such that they can be treated as constant DC voltage sources without any ripples;

4) the switching frequency fs is much higher than the line frequency such that the rectified line input voltage  $|vin (\theta)|$  is constant within a switching period.

# 5.1. Circuit Characteristics

According to Fig.4.1 (b), there is no input current drawn from the source in Mode A, and the phase angles of the dead-time  $\alpha$  and  $\beta$  can be expressed as

$$\alpha = \arcsin(\frac{V_T}{V_{pk}}) \tag{6}$$

$$\beta = \pi - \alpha = \pi - \arcsin(\frac{V_T}{V_{pk}}) \tag{7}$$

where VT is the sum of VB and Vo . Thus, the conduction angle of the converter is

$$\gamma = \beta - \alpha = \pi - 2 \arcsin(\frac{V_T}{V_{pk}})$$

(8)

From the key waveforms (see Fig. 4.3), the peak currents of the two inductors are:

$$i_{L_{1_{pk}}} = \begin{cases} \frac{v_{in}(\theta) - V_{T}}{L_{1}} d_{1}T_{s}, \alpha < \theta < \beta \\ 0, otherwise \end{cases}$$

(10)

$$I_{L2_{-}pk} = \frac{V_{B}}{L_{2}} d_{1}T_{s}$$

(11)

where Ts (1/fs) is a switching period of the converter. In (10) and (11), the dependency of iL1 pk on  $\theta$  has been omitted for clarity. It is noted that L2 does not contribute in equation (10) even though it is on the current return path of the PFC cell.

In addition, by considering volt–second balance of the L1 and L2 , respectively, the important duty ratio relationships can be expressed as follows

$$d_{2} + d_{3} = \begin{cases} \frac{V_{in}(\theta) - V_{T}}{V_{T}} d_{1}, \alpha < \theta < \beta \\ 0, otherwise \end{cases}$$

(12)

$$d_{2} = \frac{V_{B}}{V_{O}} d_{1}$$

(13)

By applying charge balance of CB over a half-line period, the bus voltage VB can be determined. From Fig. 4.3, the average current of CB over a switching and half-line periods are expressed as follows:

$$< i_{CB} >_{sw} = .5(i_{L1_{pk}}(d_1 + d_2 + d_3) - I_{L2_{pk}}d_1) < i_{CB} >_{sw} = d_1^2 T_s \frac{\left[(v_{in}(\theta) - V_T)v_{in}(\theta)\right]}{L_1 V_T} - d_1^2 T_s \left[\frac{V_B}{L_2}\right]$$

(14)

And

$$< i_{CB} >_{\pi} = \frac{1}{\pi} \int_{0}^{\pi} < i_{CB} >_{sw} d\theta$$

$$< i_{CB} >_{\pi} = \frac{d_{1}^{2} T_{s}}{2\pi} \left[ \frac{V_{pk}}{L_{1}} \left( \frac{V_{pk}}{V_{T}} \left( \frac{\gamma}{2} + \frac{A}{4} \right) - B \right) - \frac{\pi V_{B}}{L_{2}} \right]$$

(15)

where the constants A and B are

$$A = \sin(2\alpha) - \sin(2\beta)$$

$$B = \cos(\alpha) - \cos(\beta)$$

(16)

Putting equation (4.8) to zero due to the steady-state operation, this leads to

$$V_{B} = \frac{MV_{pk}^{2}}{2\pi(V_{B}+V_{O})} \left[ \pi - 2 \arcsin(\frac{V_{B}+V_{O}}{V_{pk}}) - \frac{2(V_{B}+V_{O})\sqrt{(V_{pk}+V_{B}+V_{O})(V_{pk}-V_{B}-V_{O})}}{V_{pk}^{2}} \right]$$

(17)

where M is the inductance ratio L2/L1.

As observed from equation(4.11), the bus voltage VB can be obtained easily by numerical method. It is noted that VB is independent on the load, but dependent on the inductance ratio M.. It is noted that the bus voltage is kept below 150 V at high-line input condition.

Similarly, the instantaneous and average input currents of the proposed circuit are

$$\langle i_{in} \rangle_{sw} = \frac{i_{L_{1_pk}}d_1}{2} = \begin{cases} \frac{v_{in}(\theta) - V_T}{2L_1} d_1^2 T_s, \alpha < \theta < \beta \\ 0, otherwise \end{cases}$$

(18)

And

$$I_{in} = \frac{1}{\pi} \int_{\alpha}^{\beta} \langle i_{in} \rangle_{sw} d\theta$$

$$I_{in} = \frac{d_1^2 T_s}{2\pi L_1} \left[ V_{pk} B - \gamma V_T \right]$$

(19)

Using equation (18) and (19), the rms value of the input current, average input power and power factor are given by

$$I_{in\_rms} = \sqrt{\frac{1}{\pi} \int_{\alpha}^{\beta} (\langle i_{in} \rangle_{sw})^2 d\theta}$$

$$I_{in\_rms} = \frac{d_1^2 T_s}{2\sqrt{\pi} L_1} \sqrt{V_{pk}^2 (\frac{\gamma}{2} + \frac{A}{4}) - 2V_{pk} V_T B + \gamma V_T^2}$$

$$P_{in\_} = \frac{1}{\pi} \int_{\alpha}^{\beta} V_{in}(\theta) \langle i_{in} \rangle_{sm} d\theta$$

(20)

$$\mathbf{p}_{in} = \frac{1}{\pi} \int_{\alpha} v_{in}(\theta) < i_{in} >_{sw} d\theta$$

(21)

$$P_{in} = \frac{d_{1}^{2}T_{s}V_{pk}}{2\pi L_{1}} \left[ V_{pk}(\frac{\gamma}{2} + \frac{A}{4}) - V_{T}B \right]$$

$$PF = \frac{\frac{1}{\pi}\int_{\alpha}^{\beta} v_{in}(\theta) < i_{in} >_{sw} d\theta}{\frac{V_{pk}}{\sqrt{2}} I_{in\_rms}}$$

$$PF = \sqrt{\frac{2}{\pi}} \frac{V_{pk}(\frac{\gamma}{2} + \frac{A}{4}) - V_{T}B}{\sqrt{V_{pk}^{2}}(\frac{\gamma}{2} + \frac{A}{4}) - 2V_{pk}V_{T}B + \gamma V_{T}^{2}}$$

(22)

### **5.2** Condition for DCM

To ensure both cells working in DCM mode throughout the ac line period, we must determine their critical inductance first. To allow L1 working in DCM and from equation (12), we have the following inequalities

$$d_2 + d_3 \subseteq 1 - d_{1\_PFC} \tag{23}$$

$$d_{1\_PFC} <= \begin{cases} \frac{V_T}{v_{in}(\theta)}, \alpha < \theta < \beta \\ 0, otherwise \end{cases}$$

(24)

$$d_2 \subseteq 1 - d_{1_DC/DC} \tag{25}$$

$$d_{1\_DC/DC} <= \frac{V_O}{V_O + V_B} = \frac{V_O}{V_T}$$

(26)

$$d_{1_{max}} = \begin{cases} \min(d_{1_{PFC}}, d_{1_{DC/DC}}), \alpha < \theta < \beta \\ d_{1_{DC/DC}}, otherwise \end{cases}$$

(27)

$$R_{L_{--}\min} = \frac{V_o^2}{P_o}$$

<sup>(28)</sup>

where d1 PFC is the maximum d1 of the PFC cell.

By applying input–output power balance of the PFC cell and substituting in equation (27) into equation (21), the critical inductanceL1 crit is given by

$$L_{1_{-}crit} = \frac{R_{L_{-}\min}T_{s}V_{pk}}{2\pi V_{0}^{2}} \left[ V_{pk}(\frac{\gamma}{2} + \frac{\sin(2\alpha) - \sin(2\beta)}{4}) + V_{T}(\cos(\beta) - \cos(\alpha)) \right] d_{1_{-}\max}^{2}$$

(29)

where RL min is denoted as the minimum load resistance of the converter.

For the dc/dc cell sustaining all the power to the load under DCM operation in Mode A, the critical inductance L2 crit is the smallest. Under the input–output power balance of the dc/dc cell, the critical inductance L2 crit can be determined. The input power of the dc/dc cell in Mode A is given by

$$P_{in_{DC}/DC} = \frac{V_{B}}{\pi} \int \langle i_{DC/DC} \rangle_{sw} d\theta = \frac{V_{B}^{2} T_{S} d_{1}^{2}}{2L_{2}}$$

(30)

| IJMER | ISSN: 2249-6645 |

where < idc/dc >sw is the instantaneous input current of dc/dc cell. Hence, by substituting (27) into (30), the critical inductance L2 crit is given by

$$L_{2\_crit} = \frac{R_{L\_\min} V_B^{\ 2} T_S}{2V_0^2} d_{1\_\max}^2$$

(31)

### 4.3. Capacitors Optimization

To determine the size of the intermediate bus capacitor CB, we can consider the hold-up time (thold up) of the circuit. The bus capacitor CB will sustain all the output power within t\_hold up when the ac input source is removed. In normal practice, the hold-up time is one of the ac line cycle. In addition, the maximum capacitance of CB to meet this hold-up time requirement is determined under the low-line and full output load conditions. Thus, the size of CB is expressed as follows:

$$C_B = \frac{2P_O t_{hold\_up}}{V_{B\_nomin\,al}^2 - V_{B\_min}^2}$$

(32)

where hold up time is:

$$t_{hold\_up} = \frac{\alpha}{\omega} = \arcsin(\frac{V_B + V_O}{V_{pk}})$$

(33)

Apart from the size of CB, it is noted that the line frequency ripple on the output capacitor Co is inevitable since a portion of the input power is coupled to the load directly. However, this ripple can be reduced by increasing its capacitance.

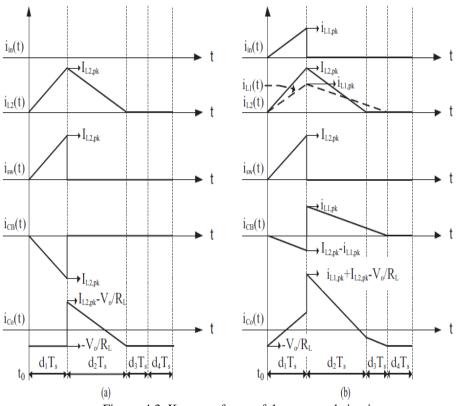

### VI. Design of the Simulation Prototype

The performance of the proposed circuit is verified by using MATLAB/ Simulink. To ensure the converter working properly with constant output voltage, a simple voltage mode control is employed. To achieve high performance of the converter for universal line operation in terms of low bus voltage (< 150V) and high power factor (> 96%), the inductance ratio has to be optimized. The lower the bus voltage of the converter, the lower voltage rating capacitor (150 V) can be used.

#### **6.1 Specifications**

output power: 100 W;

output voltage: 19 Vdc

power factor: > 96%;

intermediate bus voltage: < 150V;</li>

line input voltage: 90–270 Vrms/50 Hz;

switching frequency (fs ): 20 kHz.

M =.4

#### **6.2 Input filter**

A low-pass filter is a filter that passes low-frequency signals and attenuates (reduces the amplitude of) signals with frequencies higher than the cutoff frequency. A low-pass filter is the opposite of a high-pass filter. A band-pass filter is a combination of a low-pass and a high-pass. Low-pass filters exist in many different forms, including electronic circuits (such as a hiss filter used in audio), anti-aliasing filters for conditioning signals prior to analog-to-digital conversion, digital filters for smoothing sets of data, acoustic barriers, blurring of images, and so on. The moving average operation used in fields such as finance is a particular kind of low-pass filters. Low-pass filters provide a smoother form of a signal, removing the short-term fluctuations, and leaving the longer-term trend.

F<sub>r</sub> as the resonance frequency

$$F_r = \frac{1}{(2\pi\sqrt{L_f C_f})}$$

(34)

Assume the value of  $L_t$  and find  $C_f$

Here we take RC as 2500 Hz assume  $L_{\beta}$  as 2mH then,  $= 2\mu F$

# 6.3 Intermediate bus voltage

Equation (17) is solved by using MATLAB. m=.4; vpk= 230\*sqrt(2); vo=19; f=vb-(((m\*vpk\*vpk)/(2\*pi\*(vb+vo)))\*((pi(2\*asin((vb+vo)/vpk)))-(2\*(vb+vo)\*sqrt((vpk+vb+vo)\*(vpk-vb-vo))/(vpk\*vpk)))); df = diff (f); vb=1; for M=1:10 p=eval(f); q=eval(df); eval('vb=vb-(p/q)'); end

For input given is 230V, intermediate voltage VB obtained is 98.73V.

It is noted that VB is independent on the load, but dependent on the inductance ratio M. Depicts the relationship among VB, rms value of the line voltage, and inductance ratio M. It is noted that the bus voltage is kept below 150 V at high-line input condition.

Table 2:different intermediate voltage as input varies

| INTERMEDIATE VOLTAGE |

|----------------------|

| 32V                  |

| 98.7V                |

| 117.8V               |

|                      |

# 6.4 Intermediate capacitor

Let,

$P_{O} = 100W, V_{B_{nomin al}} = 98.7V, ripple = 40\% V_{O}, V_{B_{min}} = 98.5V, V_{O} = 19V$  then,

$V_{pk} = 230 * \sqrt{2}V = 325.26V$

$\alpha = .370$  radians

$\beta = 2.77 \, radians$

$$\gamma = 2.40 radians$$

$\omega = 2 * \pi * f = 314.15 radians / sec$

Using equation (33)

t\_holdup =1.17ms Assume ripple of about 40% of the output voltage Using equation (32) intermediate capacitor is:

CB = 5mF

## 6.5 Buck and buck- boost inductor

```

Using equation (24) and (26)

```

$$d_{1\_PFC} = \begin{cases} .362, \alpha < \theta < \beta \\ 0, otherwise \end{cases}$$

$$d_{1\_DC/DC} <= \frac{V_O}{V_O + V_B} = \frac{V_O}{V_T} = .161$$

Using equation (27) d\_max is choose as

$$d_{1_{max}} = \begin{cases} .161, \alpha < \theta < \beta \\ .161, otherwise \end{cases}$$

$$R_{L_{-min}} = \frac{V_o^2}{P_o} = 3.61\Omega$$

where RL min is denoted as the minimum load resistance of the converter.

Let,

$$V_o = 19V$$

$V_{pk} = 230 * \sqrt{2}V = 325.26V$

$\alpha = .370 radians$

$\beta = 2.77 radians$

$\gamma = 2.40 radians$

Using equation (29) and (31)

$$L_{1\_crit} = 188 \mu H$$

$$L_{2\_crit} = 63 \mu H$$

# 6.6 Output capacitor filter

Output capacitor is used to eliminate the ripple in output voltage

$$C_{o} = \frac{1}{4fR_{L}} (1 + \frac{1}{\sqrt{2}R.F})$$

(35)

$$R.F = \frac{V_{ac}}{V_{dc}} = .27$$

$$C_{o} = 5mF$$

Table 3 circuit components

| ruble 5 chedit components |        |

|---------------------------|--------|

| PARAMETERS                | VALUES |

| Input Filter Inductor     | 2 mH   |

| Input Filter Capacitor    | 2 μF   |

| Inductor L1               | 188µH  |

| Inductor L2               | 63µH   |

| Capacitor CB              | 5mF    |

| Capacitor CO              | 5mF    |

Fig 6.1: Proposed Circuit In MATLAB/Simulink

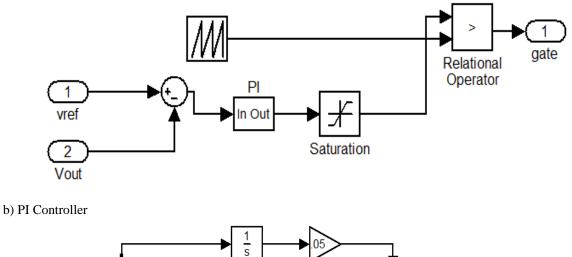

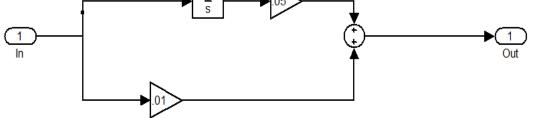

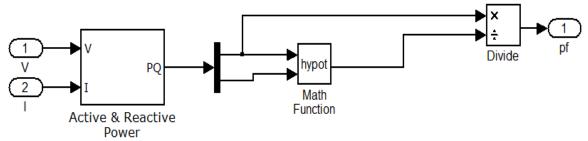

# 7.1 Subsystems

a) Pulse generating system

c) PF measurement

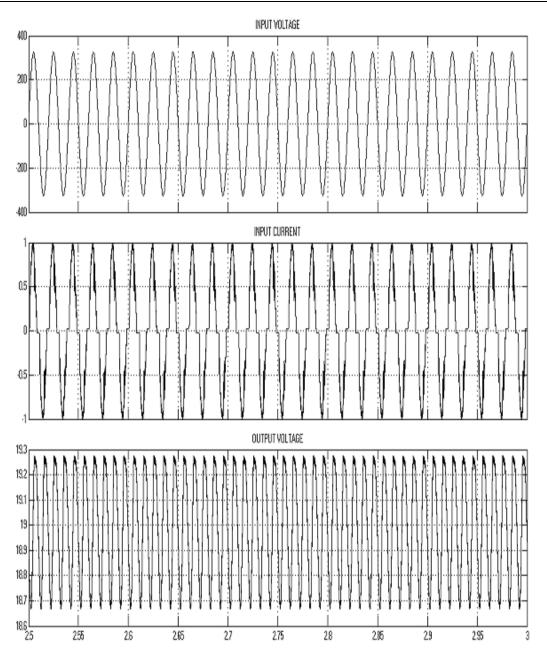

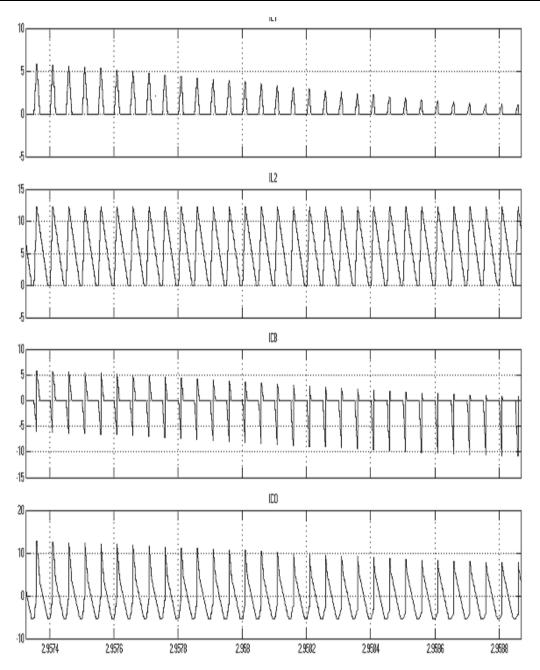

7.2 Results

Fig 6.3 waveforms of input voltage, input current,output voltage

Fig 7.4: Waveforms of IL1, IL2, ICB, ICO

# VIII. Conclusion

The proposed AC/DC converter has been simulated, and the waveforms have been observed. The intermediate bus voltage of the circuit is able to keep low at all input and output conditions and is lower than that of the most reported converters. Thus, the lower voltage rating of capacitor can be used. Moreover, the topology is able to obtain low output voltage without high step-down transformer. Owing to the absence of transformer, the demagnetizing circuit, the associated circuit dealing with leakage inductance and the cost of the proposed circuit are reduced compared with the isolated counterparts. Because of the direct power transfer path in the proposed converter, it is able to achieve high efficiency.

#### REFERENCES

- Q. Zhao, F. C. Lee, and F.-s. Tsai, "Voltage and current stress reduction in single-stage power-factor correction AC/DC converters with bulk capacitor voltage feedback," IEEE Trans. Power Electron., vol. 17, no. 4, pp. 477–484, Jul. 2002.

- [2] O. Garcia, J. A. Cobos, R. Prieto, P. Alou, and J. Uceda, "Single phase power factor correction: A survey," IEEE Trans. Power Electron., vol. 18, no. 3, pp. 749–755, May 2003.

- [3] S. Luo,W. Qiu,W.Wu, and I. Batarseh, "Flyboost power factor correction cell and a new family of single-stage AC/DC converters," IEEE Trans. Power Electron., vol. 20, no. 1, pp. 25–34, Jan. 2005.

- [4] D. D. C. Lu, H. H. C. Iu, and V. Pjevalica, "A Single-Stage AC/D converter with high power factor, regulated bus voltage, and output voltage," IEEE Trans. Power Electron., vol. 23, no. 1, pp. 218–228, Jan. 2008.

- [5] M. K. H. Cheung, M. H. L. Chow, and C. K. Tse, "Practical design and evaluation of a 1 kW PFC power supply based on reduced redundant power processing principle," IEEE Trans. Ind. Electron., vol. 55, no. 2, pp. 665–673, Feb. 2008.

- [6] D. D. C. Lu, H. H. C. Iu, and V. Pjevalica, "Single-Stage AC/DC Boost: Forward converter with high power factor and regulated bus and output voltages," IEEE Trans. Ind. Electron., vol. 56, no. 6, pp. 2128–2132, Jun. 2009.

- [7] H.-Y. Li and H.-C. Chen, "Dynamic modeling and controller design for a single-stage single-switch parallel boostflyback-flyback converter," IEEE Trans. Power Electron., vol. 27, no. 2, pp. 816–827, Feb. 2012.

- [8] R. Redl and L. Balogh, "Design considerations for single-stage isolated power-factor-corrected power supplies with fast regulation of the output voltage," in Proc. IEEE Appl. Power Electron. Conf. Expo., 1995, vol. 1, pp. 454–458.

- [9] L. Antonio, B. Andrs, S. Marina, S. Vicente, and O. Emilio, "New power factor correction AC-DC converter with reduced storage capacitor voltage," IEEE Trans. Ind. Electron., vol. 54, no. 1, pp. 384–397, Feb. 2007.

- [10] E. H. Ismail, A. J. Sabzali, and M. A. Al-Saffar, "Buck-boost-type unity power factor rectifier with extended voltage conversion ratio," IEEE Trans. Ind. Electron., vol. 55, no. 3, pp. 1123–1132, Mar. 2008.

- [11] M. Ryu, J. Baek, J. Kim, S. Park, and H. Kim, "Electrolytic capacitor-less, nonisolated PFC converter for high-voltage LEDs driving," in Proc. IEEE Int. Conf. Power Electron. and ECCE Asia, 2011, pp. 499–506.

- [12] A. A. Badin and I. Barbi, "Unity power factor isolated three-phase rectifier with two single-phase buck rectifiers based on the scott transformer," IEEE Trans. Power Electron., vol. 26, no. 9, pp. 2688–2696, Sep. 2011.

- [13] S. K. Ki and D. D. C. Lu, "Implementation of an efficient transformerless single-stage single-switch ac/dc converter," IEEE Trans. Ind. Electron., vol. 57, no. 12, pp. 4095–4105, Dec. 2010.

- [14] A. Abramovitz and K. M. Smedley, "Analysis and design of a tappedinductor buck-boost PFC rectifier with low bus voltage," IEEE Trans. Power Electron., vol. 26, no. 9, pp. 2637–2649, Sep. 2011.

- [15] J. M. Alonso, M. A. Dalla Costa, and C. Ordiz, "Integrated buck-flyback converter as a high-power-factor off-line power supply," IEEE Trans. Ind. Electron., vol. 55, no. 3, pp. 1090–1100, Mar. 2008.

- [16] K. Nishimura, K. Hirachi, S. Komiyama, and M. Nakaoka, "Two buck choppers built-in single phase one stage PFC converter with reduced DC voltage ripple and its specific control scheme," in Proc. IEEE Appl. Power Electron. Conf. Expo., 2008, pp. 1378–1383.

- [17] T. J. Liang, L. S. Yang, and J. F. Chen, "Analysis and design of a single phase ac/dc step-down converter for universal input voltage," IET Electr. Power Appl., vol. 1, no. 5, pp. 778–784, Sep. 2007.

- [18] M. A. Al-Saffar, E. H. Ismail, and A. J. Sabzali, "Integrated buck-boost-quadratic buck PFC rectifier for universal input applications," IEEE Trans. Power Electron., vol. 24, no. 12, pp. 2886–2896, Dec. 2009.

- [19] X. Qu, S.-C. Wong, and C. K. Tse, "Resonance-assisted buck converter for offline driving of power LED replacement lamps," IEEE Trans. Power Electron., vol. 26, no. 2, pp. 532–540, Feb. 2011.

- [20] Y. Jang and M. M. Jovanovic, "Bridgeless high-power-factor buck converter," IEEE Trans. Power Electron., vol. 26, no. 2, pp. 602–611, Feb. 2011.

- [21] O. Garcia, J. A. Cobos, R. Prieto, P. Alou, and J. Uceda, "An alternative to supply DC voltages with high power factor," IEEE Trans. Ind. Electron., vol. 46, no. 4, pp. 703–709, Aug. 1999.